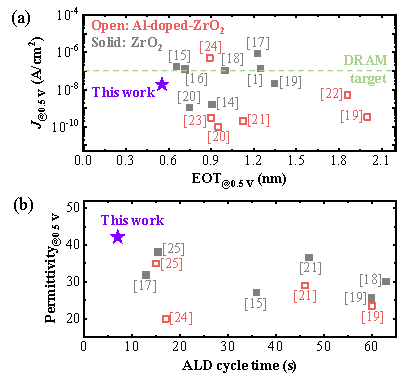

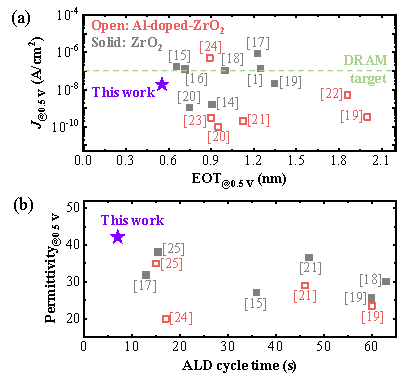

近日,中國科學技術大學微電子學院龍世兵教授課題組在ZrO?介質電容器原子層沉積?(ALD) 制備研究方面取得了新的進展。近年來DRAM特征尺寸逐步微縮,保持電容器的高電容值和低漏電的需求日益緊迫,對 high-k低漏電介質材料的制備要求日益增高,高性能電容器制備成為阻礙 DRAM 技術更進一步的關鍵問題。本工作提出了一種全新的“短脈沖?- 高通氧量”的ALD生長方式,調控介質中鋯氧比例,提高了介質 k 值,同時降低了漏電。相關成果以“Oxidizer Engineering of ALD for Efficient?Production of ZrO??Capacitors in DRAM”為題發表于電子器件領域知名期刊?IEEE Electron Device Letters。DRAM電容器介質材料等效氧化物厚度(EOT)逐步微縮,給介質生長帶來了挑戰。這項研究系統地控制了介電薄膜ALD生長過程中的氧化劑?(O?)?通量,發現高氧通量可以補償短脈沖時間帶來的負面影響。這種“短脈沖?- 高通氧量”方法可以實現高?k (~47)、低漏電?(2 × 10???A/cm2,DRAM?工作電壓約為 0.5 V)?電容器的制備,有效降低了器件EOT (~0.55 nm),同時減少了 ALD?生長介質循環周期時間,提高了DRAM生產效率。與其他報道中鋯基器件性能的對比見圖1。

圖1. (a)J@V=0.5 V與EOT的關系圖,對比了本工作與其他報告中的鋯基器件性能。值得注意的是,本工作最低EOT可達?0.55 nm,在其中性能最優。(b)ALD循環時間與 k 值報道的關系圖,顯示出“短脈沖?- 高通氧量”方法的優越性。

?

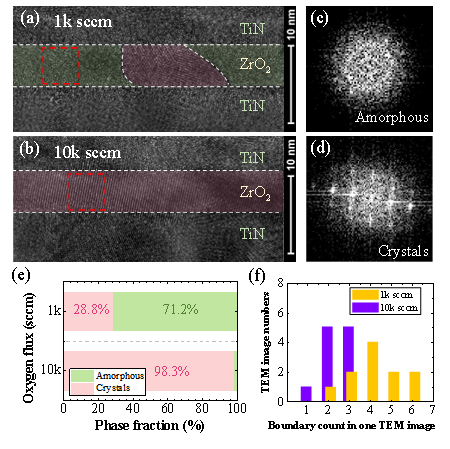

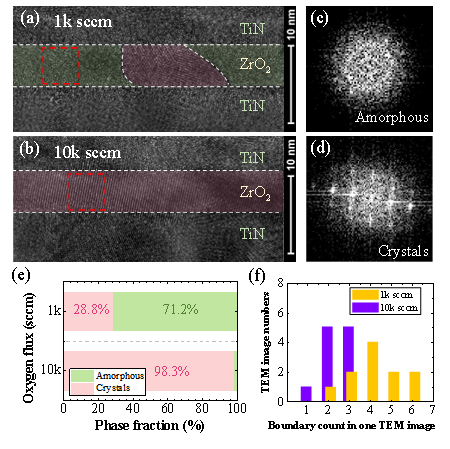

高分辨率透射電子顯微鏡測試結果以及分析揭示了 k 值升高以及漏電降低的機制。從圖2中可見,隨著氧通量的升高,介質結晶程度升高,k 值隨之提升;與此同時,結晶程度的提升使得晶界數量減少,從而改善了器件的漏電。

圖2. 高分辨率透射電子顯微鏡?(HRTEM) 下6 nm ZrO?薄膜器件橫截面的圖像。1k (a) 和 10k (b) sccm氧通量,顯示了非晶態(c,綠色區域)和結晶態(d,粉紅色區域)?部分。對不同氧通量樣品進行結晶程度的統計,可以看到高氧通量樣品結晶程度高(e),且晶界數量較少(f)。

?

學院博士生唐心怡為論文第一作者,學院特任教授呂頔和執行院長龍世兵教授為論文通訊作者。此項研究工作得到了國家自然科學基金委區域聯合基金項目(U20A20207)的資助,也得到了中國科大微納研究與制造中心的支持。

文章鏈接:DOI:?10.1109/LED.2024.3455338

https://ieeexplore.ieee.org/document/10669047

?

(微電子學院)

?

?

原文始發于微信公眾號(中國科大微電子學院):我院在超薄ZrO?介質薄膜制備研究中取得新進展