?

聊到混合鍵合(Hybrid Bonding), 我們在之前的一篇文章《先進封裝之混合鍵合(Hybrid Bonding)的前世今生》已經對其進行了簡要介紹,此處不再贅述。

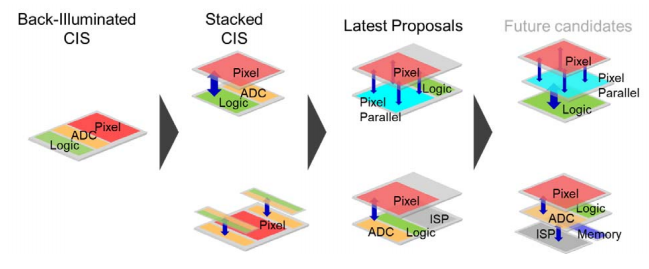

Hybrid Bonding從最初量產便首先應用于圖像傳感器上,直到現在除了一些先進處理器在應用該技術外,其在圖像傳感器CIS(CMOS image sensors)上仍然在不斷的發展,最終產品常被用于高端手機相機、數碼相機和數碼單反相機的堆疊背照式CMOS圖像傳感器(BI-CIS)。

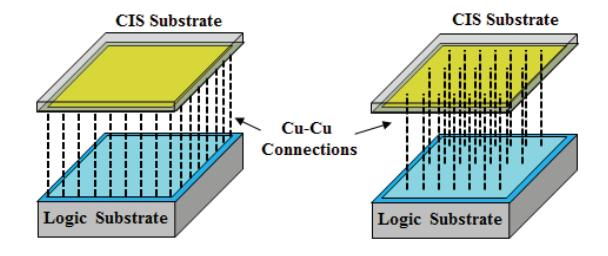

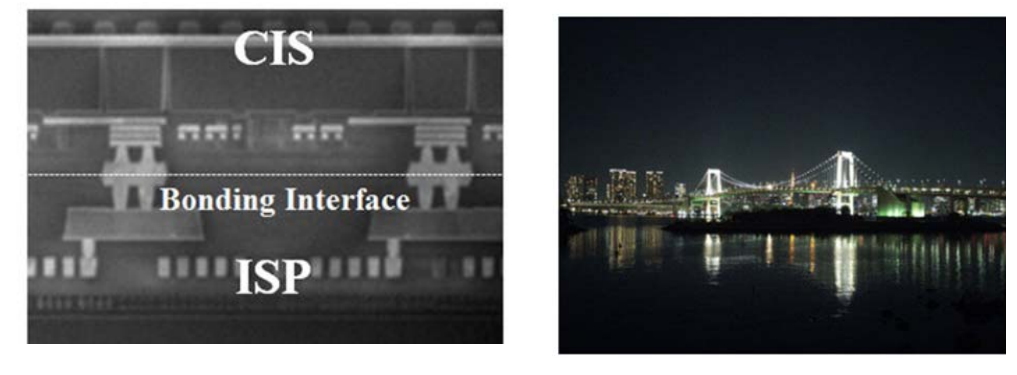

今天,我們聊聊日本Sony發布的一種BI-CIS技術,其目的是將圖像傳感器(CIS)和圖像信號處理器(ISP)連接在一起。如圖1(左)所示,傳統的BI-CIS采用TSV技術將像素陣列和邏輯電路在芯片外圍區域實現6微米間距,2萬個銅-銅連接。圖1(右)采用了銅-銅混合鍵合的BI-CIS器件則是實現了的更小的互聯間距(5微米間距)和更大規模的互聯,達到150萬個銅柱連接。更高的密度甚至可以做到3微米和300萬個銅柱連接。

圖1,傳統堆疊BI-CIS(左)

和帶有銅-銅連接的新堆疊BI-CIS(右)

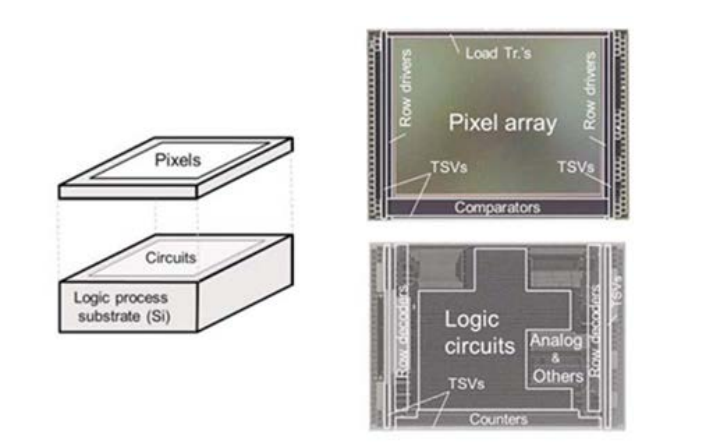

圖2,傳統堆疊BI-CIS實物圖,采用TSV技術

傳統TSV技術與銅-銅混合鍵合的主要差異如圖4所示。明顯可以看出銅-銅混合鍵合技術中單個連接單元占用空間更小。從布局靈活性的角度來看,與傳統的芯片堆疊技術(如通過硅通孔技術)相比,銅-銅連接具有許多優點。我們可以將銅-銅連接放置在上/下芯片的外圍區域以及中央區域這樣就增加了電路設計的靈活性。鍵合步驟示意圖如圖5所示。

圖4,帶有TSV的鍵合基板的示意圖(上)

和帶有混合鍵合的鍵合基板的示意圖(下)

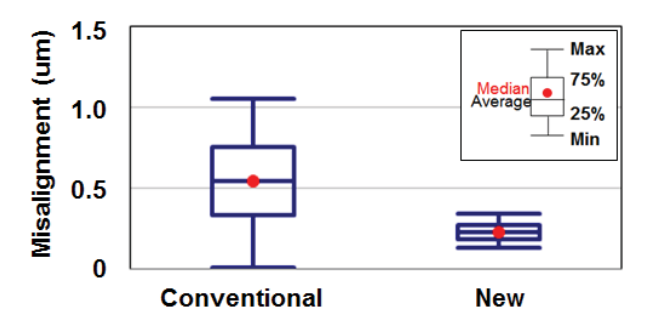

這么小的間距,勢必要求更高的貼裝精度,圖6為傳統鍵合工藝(左)和最新鍵合工藝(右)制造中的錯位比較。可以看到0.5微米以下的錯位是完全可以做到的。

和最新鍵合工藝(右)制造中的錯位比較

這些是不是已經夠復雜了?還有更為復雜更先進的封裝技術應用于CIS產品。業界提出了具有兩種類型的3D堆疊結構:同質芯片堆疊和異質芯片堆疊。當然,在任何結構中,具有高密度連接的三個或更多芯片將是突破傳統設備的關鍵。

在3D堆疊器件中,正面對正面的銅-銅混合鍵合和正面面對背面的銅-銅混合鍵合為我們提供了三維集成的靈活性。相比傳統的微凸點技術,晶圓級銅-銅混合鍵合可以在極高密度下電連接上下芯片。

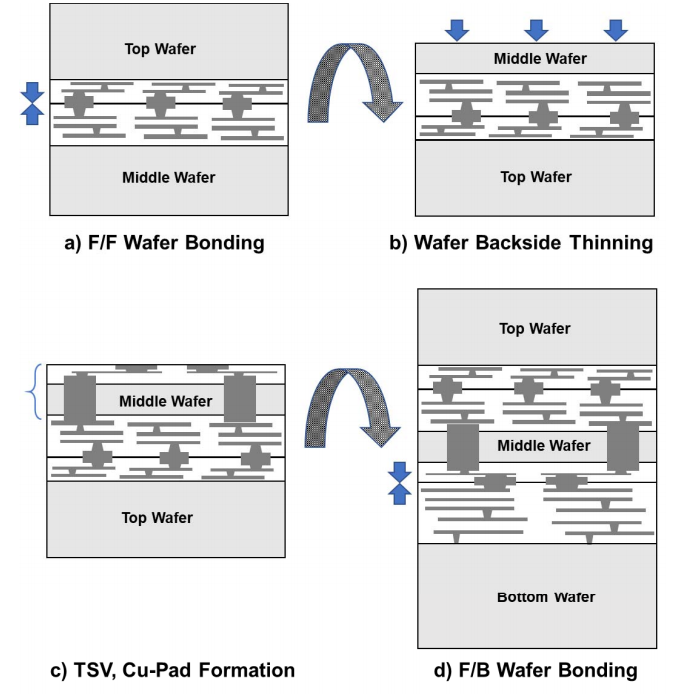

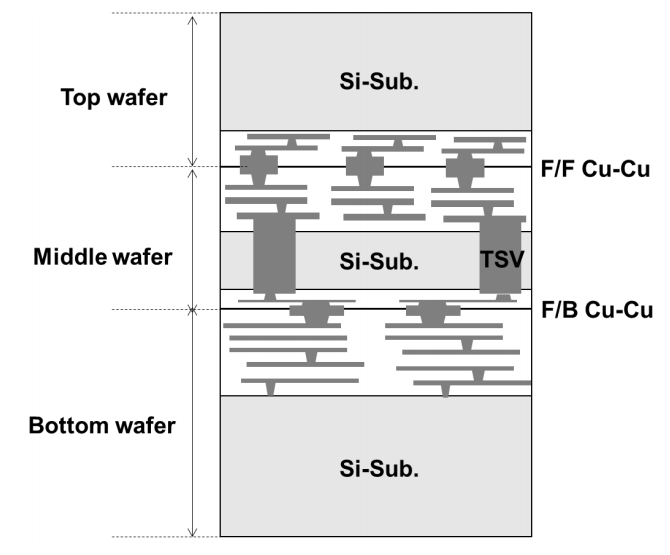

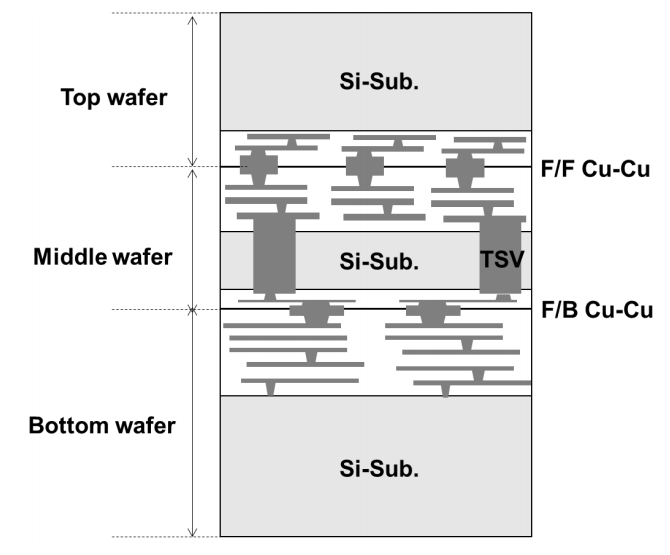

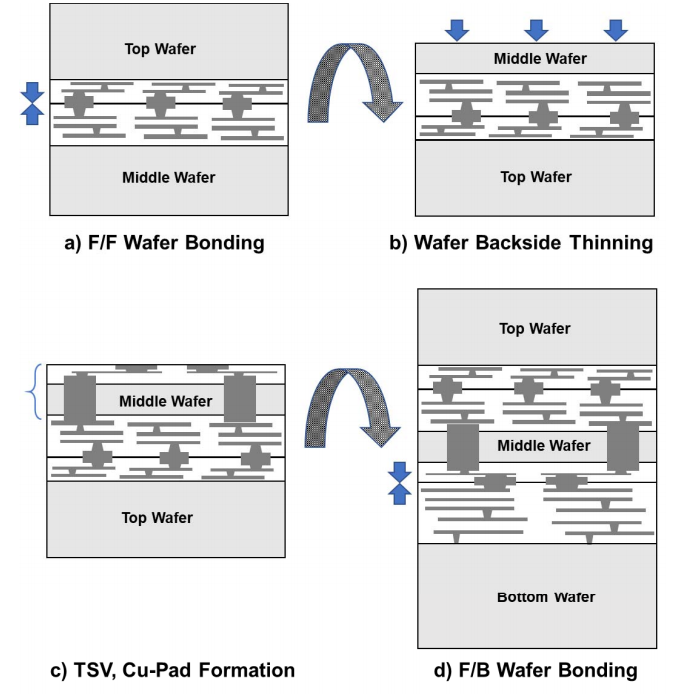

圖8,展示了一個三層堆疊結構的示例。其具體加工流程如圖9所示。首先,在top wafer和middle wafer的頂部BEOL層上制作銅連接BUMP。將top wafer和middle wafer進行面對面的銅-銅混合鍵合后,middle wafer的背面通過減薄以制作TSV。最后,通過位于middle wafer背面和bottom wafer頂部BEOL層上制作的銅連接bump,實現middle wafer和bottom wafer的銅-銅混合鍵合。

圖8,三層堆疊結構的示例

本文介紹的技術當前主要來自于日本Sony公司,國內同行對相關技術的報道還不多。希望國內封裝巨頭們,也抓緊趕上。

參考文獻:

1. The Scaling of Cu-Cu Hybrid Bonding For High Density 3D Chip Stacking Y. Kagawa , S. Hida etc.

2. Novel Stacked CMOS Image Sensor with Advanced Cu2Cu Hybrid Bonding Y. Kagawa , N. Fujii,etc.

3. An Advanced CuCu Hybrid Bonding For Novel Stacked CMOS Image Sensor Y. Kagawa, N. Fujii, etc.

4. Impacts of Misalignment on 1μm Pitch Cu-Cu Hybrid Bonding Y. Kagawa, H. Hashiguchi, etc

5. Development of face-to-face and face-to-back ultra-fine pitch Cu-Cu hybrid bonding Yoshihisa Kagawa, Takumi Kamibayashi, etc.

原文始發于微信公眾號(艾邦半導體網):先進封裝之圖像傳感器混合鍵合(CMOS Hybrid Bonding)