?

?

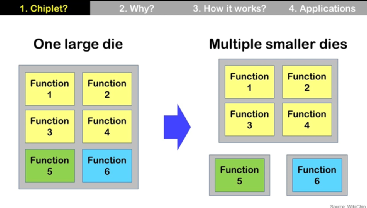

大家好,歡迎來到半導體內(nèi)容。我接到一個講講關(guān)于Chiplet的請求,所以今天的話題是Chiplet。我們來談?wù)劙伞hiplet是一種半導體技術(shù),使用多種小芯粒來實現(xiàn)目標功能,將原本應(yīng)該由一個芯粒來完成的任務(wù),分為多種較小的芯粒集成在一起來實現(xiàn)。從而,減少產(chǎn)品開發(fā)時間和成本。Chiplet不是指封裝類型,它是封裝架構(gòu)的一部分。通過chiplet,多種芯粒可以集成到現(xiàn)有的封裝類型中,例如2.5D、3D、扇出及多芯片模塊。

?

觀看視頻

?

想象一下,我們有一個大芯片,它有CPU,GPU,RAM及其它功能塊都在一個芯片中作為SOC系統(tǒng)芯片。但這是非常昂貴的,并且有許多挑戰(zhàn)使這些產(chǎn)品很難量產(chǎn)。幸運的是,我們可以通過多種較小的芯粒來實現(xiàn)所有這些功能,而且這樣在成本上更合理。但是由于我們需要在每個芯粒上添加接口模塊,所以總的所有芯粒總面積將超過全部集成在一個芯片上。這是chiplet的一個簡單概念。因此,Chiplet是大型系統(tǒng)集成芯片的良好解決方案,通常用于高性能計算,而不是智能手機中的小芯片。一種使用先進的半導體制程如45nm、16nm甚至7nm。

?

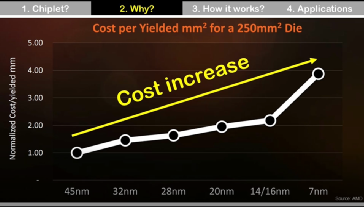

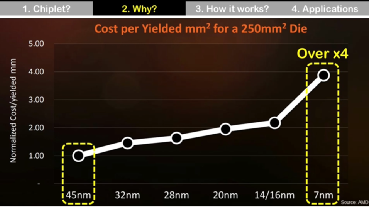

隨著大芯粒的成本繼續(xù)增加。針對一個250mm2尺寸的芯粒,14或16納米制程的成本是相同尺寸的45納米芯片的2倍以上。而7納米芯片比45納米芯片貴4倍以上。而到我們最近談?wù)摰?納米甚至3納米,成本更將不斷增加。這意味著使用先進制程制造大型SoC芯片正在失去其經(jīng)濟效益。這就是為什么這個行業(yè)又開始使用chiplet了。

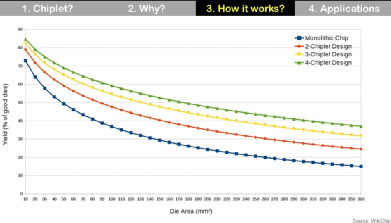

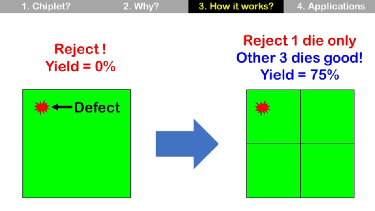

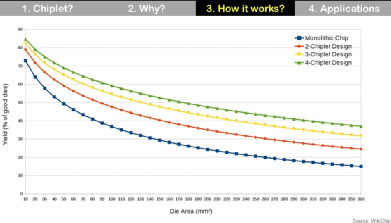

Chiplet是將大型的單一芯粒分解成多個較小的芯粒。它是如何工作的?這是一個大芯粒和4個小芯粒之間的簡單比較。如果在芯粒的左上角有缺陷,則整個芯粒就無法使用,所以良率是0。如果我們有4個小芯粒,并且在完全相同的位置存在相同的缺陷。然后4個芯粒只有一個不能使用,良率為75%。這意味著我們?nèi)匀豢梢怨?jié)省3個芯粒。它也適用于邊緣DIE。在左邊,我們有大量無法使用的邊緣DIE。在右邊,我們也有相類似的損失,但較小的芯粒比較大的芯粒具有更高的良率。這是一個芯粒與chiplet 的有2,3或4個芯粒之間的比較。對于360mm2的一個芯粒,我們僅有15%的良率。但針對4個芯粒的chiplet 設(shè)計,良率將是前者的一倍以上。即使4個芯粒的chiplet 設(shè)計的總面積比一個大芯粒多出10%,Chiplet的設(shè)計明顯提高了良率和合理性。

?

?

?

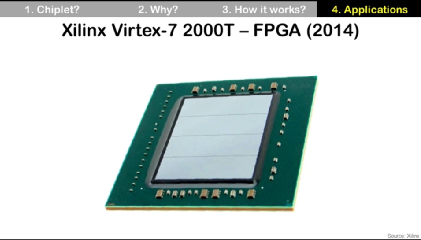

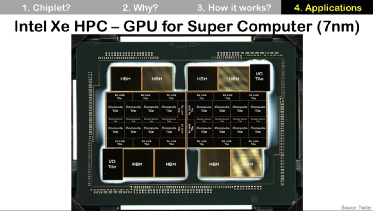

早在2014年,賽靈思生產(chǎn)的72000,它使用了4個較小的芯粒,而不是1個大芯片。這是AMD史詩級般的第二代封裝,它是使用7nm的服務(wù)器CPU。其封裝尺寸為58.5mm乘75.4mm,它非常大。中心有8個使用7nm技術(shù)的CPU和一個I/O 芯片使用14nm技術(shù)。這是英特爾XE HPC,它里面的GPU使用7nm技術(shù),現(xiàn)在英特爾只在實驗室中使用它。它有47個組件,包括2個基礎(chǔ)芯片使用英特爾10nm技術(shù)。16個計算核心使用TSMC的7納米技術(shù)。

?

?

11個緩沖使用英特爾十納米技術(shù),2 個I/O芯粒由代工廠代工。8個HBM存儲器堆棧由存儲廠加工。沒有chiplet技術(shù),是不可能將47個芯粒的功能一次性在單個芯片上加工完成的。盡管chiplet有很多好處,但它也有一些挑戰(zhàn)。我們需要思考芯片到芯片的互連,芯片設(shè)計師和封裝設(shè)計師的協(xié)同,多個小芯粒的測試也將非常不同于一個大芯粒的測試等。

?

觀看視頻

來源:youtube semicon talk

?

原文始發(fā)于微信公眾號(艾邦半導體網(wǎng)):先進封裝Chiplet 技術(shù)介紹(視頻)