目錄

一.關(guān)于先進(jìn)封裝的碎碎念

二.2.5D先進(jìn)封裝

1.2.5D先進(jìn)封裝是啥

2.英特爾與臺(tái)積電、日月光、Amkor在這一領(lǐng)域的布局

3.EMIB與EFB、CoWoS的產(chǎn)業(yè)邏輯

4.區(qū)分InFO與CoWoS

5.關(guān)于M1U的雜談

6.Si-Fi技術(shù)

三.3D先進(jìn)封裝

1.定義與限制條件(排除MEMS和CIS)

2.關(guān)于3D Cahce的誤會(huì)

3.關(guān)鍵技術(shù)——令人痛恨的TSV

4.關(guān)鍵技術(shù)——混合鍵合

5.英特爾和他的TCB

四.未來(lái)

1.臺(tái)積電的野望

2.嵌埋式封裝

PS:分了好久用零碎時(shí)間寫的,所以一些術(shù)語(yǔ)可能前后對(duì)不上,反正基板=載板,轉(zhuǎn)接板=中介層,

.一.關(guān)于先進(jìn)封裝的碎碎念

?

不知不覺寫了這么多,為了避免歧義,本文討論的2.5D/3D都是指在中段完成封裝的東西,一些后段堆疊的封裝不再討論之列(比如單獨(dú)的PoP封裝)。談2.5D/3D先進(jìn)封裝之前,再嘴碎多說(shuō)幾句,本文就是業(yè)務(wù)時(shí)間寫的雜談性質(zhì)的文章,難免有疏漏,歡迎評(píng)論or私信指出,而且一篇文章要扯這么多內(nèi)容肯定有很多覆蓋不到的地方,僅僅是一個(gè)拋磚引玉的作用,有興趣的多去外網(wǎng)查查資料。然后再瞎扯之前,先拋出兩個(gè)觀點(diǎn):1.半導(dǎo)體行業(yè)很多時(shí)候并不是看技術(shù)先進(jìn)與否,成本、商業(yè)模式和自身利益才是這幫人更優(yōu)先考慮的,理解了這一點(diǎn)就能明白為什么有的企業(yè)要做一些”與眾不同“的操作。2.封裝演進(jìn)的本質(zhì)是在成本可控的情況下盡可能提升互聯(lián)的密度與速度,所以先進(jìn)封裝并不是靈丹妙藥,如果你造不出一個(gè)合格的SoC/chiplet,那用上什么封裝都是白搭。

PS:下文可能比較少提到amkor和大陸封裝廠,因?yàn)槲沂稚详P(guān)于它們的資料很少,我就選擇性忽略了

二.2.5D先進(jìn)封裝

1.2.5D先進(jìn)封裝是啥

經(jīng)典的帶Interposer(中介層、轉(zhuǎn)接板隨你怎么叫)的2.5D封裝

2.5D封裝第一次走入大眾視野應(yīng)該是AMD的15年發(fā)布的的fury顯卡,配合了4GB HBM顯存(以前主要是一些遠(yuǎn)離消費(fèi)領(lǐng)域的FPGA和ASIC使用過),在這之后,2.5D封裝常常與HBM捆綁,頻頻出現(xiàn)在顯卡、ASIC和FPGA上,但是從定義上,其實(shí)業(yè)界一直沒有給出2.5D封裝的嚴(yán)格定義,2.5D封裝也不像3D封裝那么直白,它其實(shí)有好多種形式,為了方便下文說(shuō)明,我這里簡(jiǎn)單給2.5D封裝做一個(gè)”定義“,2.5D封裝指的是芯片/chiplet之間通過轉(zhuǎn)接板(或者叫中介層)、硅橋、高密度RDL或者任何I/O密度遠(yuǎn)高于ABF載板的互聯(lián)手段的封裝,核心是兩點(diǎn):1.多die集成;2.互聯(lián)部分引入高I/O密度的”介質(zhì)“而不是依靠載板上走線,除此之外,用不用TSV、中介層是什么材質(zhì)啥的不影響,基于這兩點(diǎn),我們?cè)谑忻嫔媳容^常聽到的2.5D封裝有CoWoS(廢話)、EMIB、高密度和LSI版本的FoCoS三種,正好對(duì)用了2.5D封裝的三大類:1.互聯(lián)層是整塊轉(zhuǎn)接板,2.互連層是一小塊硅橋,3.互連層是高密度RDL或者RDL中的硅橋。

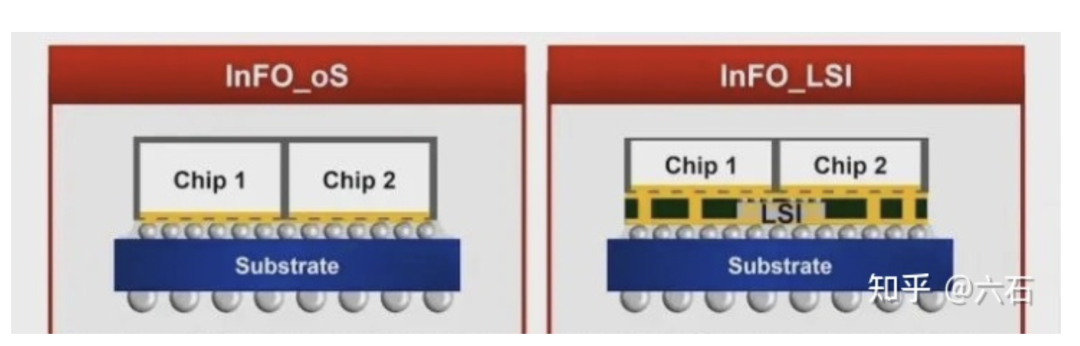

PS:InFO能不能算2.5D封裝?InFO其實(shí)有好多種,如果是A系列用的那種只封單die的普通晶圓級(jí)扇出封裝,應(yīng)該是不能算,但是如果是多芯片封裝然后RDL層IO密度高有硅橋的InFO(InFO-oS、InFO-LSI和部分InFO-MCM)算是2.5D封裝,同理可以推廣到FoCoS等扇出技術(shù)上。如何快速辨別呢?有個(gè)小把戲就是看它RDL層底下需不需要載板,需要的話就是2.5D封裝(大概率)。

PS2:AMD在目前ZEN處理器上用的是2.5D封裝嗎?這里注意區(qū)分一下chiplet和2.5D封裝,這兩個(gè)概念是分開的,有些文章把他們劃了等號(hào),chiplet目前更多是一種設(shè)計(jì)理念,ZEN系列使用了chiplet,不算用了2.5D封裝。

2.英特爾與臺(tái)積電、日月光、Amkor在這一領(lǐng)域的布局

我覺得沒什么好一一介紹的,干脆寫個(gè)"等式",然后講講里面比較”特殊“的EMIB和InFO-SoW。

2.5D封裝可以簡(jiǎn)單分成3種:

1.一整塊硅/玻璃等做中介層,所有芯片放在這個(gè)中介層上,性能在大多數(shù)情況下可以說(shuō)是最好的,缺點(diǎn)也很明顯,太貴了,目前這個(gè)技術(shù)除了英特爾,每家都有實(shí)際商用的,最典型的就是臺(tái)積電的CoWoS-S=各家名叫2.5D interposer的封裝技術(shù)

2.使用硅橋互聯(lián),這幾乎是目前性能與成本最平衡的技術(shù),但是除英特爾以外的廠商應(yīng)用的時(shí)間節(jié)點(diǎn)更晚,基本上臺(tái)積電的InFO-LSI=日月光的FOCoS-LSI=安靠S-cennect≈EMIB,EMIB比較特殊,下文會(huì)重點(diǎn)講一下。

3.使用高密度RDL層互聯(lián),這幾年有所突破的一個(gè)技術(shù),通過SAP加成法沉積銅線路而非Embedded法,實(shí)現(xiàn)了高布線密度而高I/O密度,一定程度上能替代整塊的轉(zhuǎn)接板(高密度RDL以后有機(jī)會(huì)另開文章說(shuō),相關(guān)的論文還沒看完

),基本上臺(tái)積電的CoWoS-R≈InFO-oS=日月光的FoCoS高密度版本=安靠S-Swift。

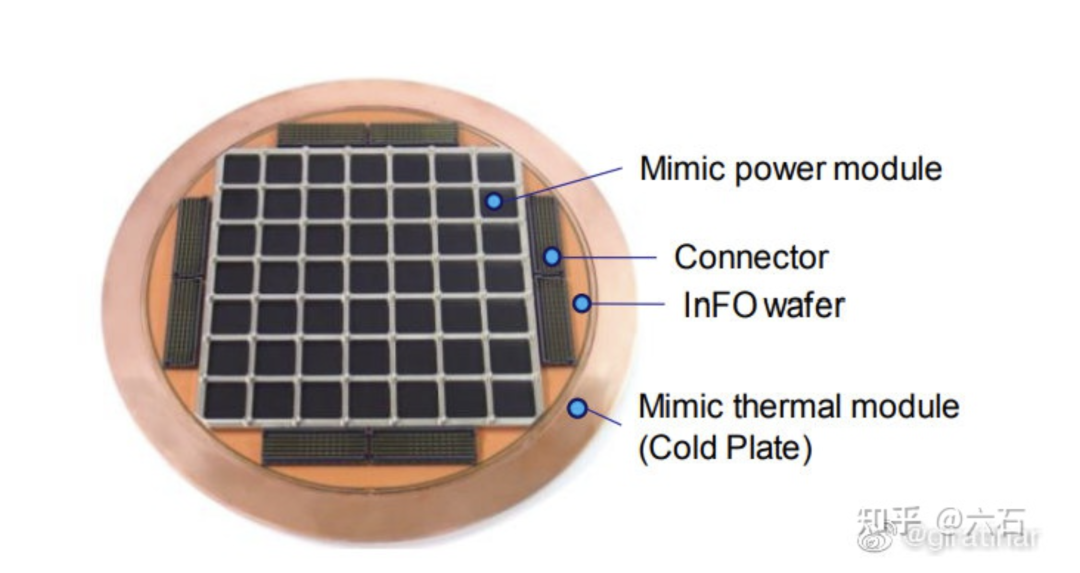

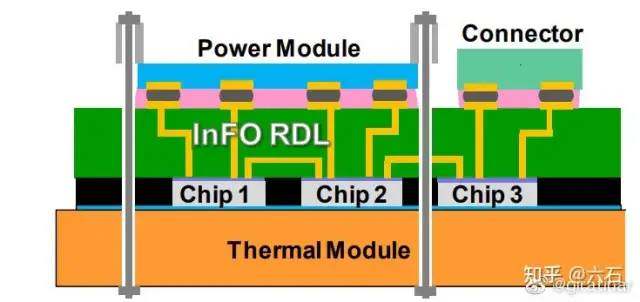

4.論外:InFO-SoW,本質(zhì)上也是高密度RDL互聯(lián),但是,是什么樣瘋狂的靈魂要搞出這種東西

可以說(shuō)風(fēng)格也和第一個(gè)用上它的客戶特斯拉很符合了。

盤子那么大的芯片你怕不怕!

在之前寫扇出封裝的文章里,我覺得InFO-SoW只是實(shí)驗(yàn)室對(duì)封裝尺寸的極限探索所以沒有介紹,后來(lái)特斯拉用Dojo打了我的臉。一句話總結(jié)InFO-SoW就是既然這世界上有cerebras這樣想做超大芯片的人,就有想做超大封裝的人

,InFO-SoW就是面向大規(guī)模MCM而生的,它把芯片陣列用晶圓級(jí)的RDL層連接在一起,還集成了功率模塊、互聯(lián)單元和“晶圓級(jí)”的均熱板(如上圖),實(shí)現(xiàn)了system on wafer,InFO-SoW封裝甚至把基板、PCB都給去掉了,成品就是一個(gè)用金屬架子支撐結(jié)構(gòu)的大盤子

直接就可以放在模塊里用了。

灰色的豎線是為了支撐這個(gè)大餅的結(jié)構(gòu)件

為什么臺(tái)積電會(huì)想搞這樣一個(gè)玩意?我們回看現(xiàn)在基于基板甚至板級(jí)的MCM封裝,有一個(gè)很大的問題就是怎么解決C2C(chip to chip)的互聯(lián),基板上互聯(lián)最直接粗暴,但是高層數(shù)ABF基板可憐的良率和成本并不能支撐你去做一個(gè)大規(guī)模的MCM,同時(shí)該死的趨膚效應(yīng)會(huì)給你的信號(hào)傳輸帶來(lái)巨大的困擾,更不要說(shuō)板級(jí)MCM了,而硅中階層的方法好是好,但是太貴了,如果真要做一個(gè)芯片陣列級(jí)別的MCM封裝,成本吃不開,InFO-SoW的解決方法就是懟了6層的RDL,讓布線空間充足無(wú)比,信號(hào)完整性和功耗表現(xiàn)也更好,同時(shí)直接在芯片封裝成品的邊緣上方放置了Conenctor單元方便與外界互聯(lián),power單元也直接懟在芯片正上方,真的是大力出奇跡的典范。

因?yàn)槊嫦蚋咝阅茴I(lǐng)域尤其是AI應(yīng)用,InFO-SoW設(shè)計(jì)之初就沒有考慮過風(fēng)冷,直接上了水冷散熱,臺(tái)積電的給原型產(chǎn)品設(shè)計(jì)的最大散熱功耗可以達(dá)到7000W,可以說(shuō)是非常兇猛了

3.EMIB與EFB、CoWoS的產(chǎn)業(yè)邏輯

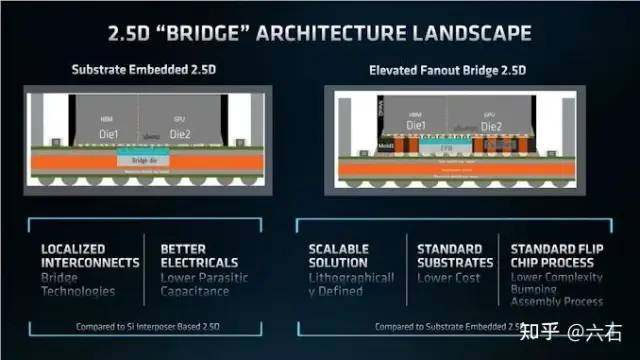

EMIB是一個(gè)很有趣的東西,它能夠達(dá)成和使用整塊硅中介層差不多的性能,也不需要像中介層打大量的TSV(在后續(xù)部分我們會(huì)聊一下為啥TSV這么令人討厭),使得硅橋本身的制作工藝更簡(jiǎn)單,成本也更低,并且引入硅橋之后,原本需要10層以上的ABF基板可以較少到7層甚至4層,這對(duì)節(jié)約ABF基板成本幫助很大(10層板良率不到50%,每多一層良率還要下降),因此英特爾這么多年”懶得“使用硅中介層這種技術(shù)。本質(zhì)上EMIB它也是一種硅橋技術(shù),但是和AMD展示的EFB、InFO-LSI不同,它的硅橋是嵌埋式的,硅橋互聯(lián)最早在2011年由英特爾提出,然后在2016年這個(gè)技術(shù)變成了現(xiàn)在EMIB,擁有了嵌埋的概念。之后EMIB逐步被英特爾拿來(lái)主要在服務(wù)器端使用,EMIB可以無(wú)視光刻曝光的尺寸限制(硅中介層面臨這個(gè)問題的,蘋果的專利里有探討類似的內(nèi)容),可以隨意在橫向擴(kuò)展各式各樣的芯片,屬于好用又”便宜“的玩意,那么為啥嵌埋式硅橋或者說(shuō)硅橋這么好用,臺(tái)積電、日月光沒有第一時(shí)間跟進(jìn)呢?答案是各家的商業(yè)模式?jīng)Q定的,下面以EFB為例探討一下這個(gè)問題。

其實(shí)AMD這圖夸了右邊的EMIB很多

AMD在MI250X上展示的EFB應(yīng)該就是和 InFO-LSI或者FoCoS-LSI的改型(大概率是后者,日月光的定制版本),兩個(gè)硅橋技術(shù)的區(qū)別就是一個(gè)會(huì)對(duì)載板進(jìn)行加工并且是嵌入在載板中的,一個(gè)不需要?jiǎng)踊澹麄€(gè)硅橋是在RDL層之中的, 然后EFB是平面工藝,這意味這它可以使用標(biāo)準(zhǔn)的FC封裝,這里的使用標(biāo)準(zhǔn)FC封裝其實(shí)是指芯片完成與EFB合封之后可以用FC貼到基板上,這樣在后道的基板級(jí)封裝上靈活性就比EMIB好很多(方便換廠商),也不用尋找能做嵌埋硅橋的基板廠商,另外EFB因?yàn)槎嗔艘粚覴DL層調(diào)高了芯片整體的高度,所以die需要做更進(jìn)一步的減薄。

這么來(lái)看,EFB是個(gè)好技術(shù),蘋果M1U也采用了類似的技術(shù),但是之前為啥除了英特爾以外沒什么人用?更別說(shuō)EMIB這類嵌埋式硅橋了,按理說(shuō)弄個(gè)硅橋?qū)Υ蠹襾?lái)說(shuō)都不難啊?問題其實(shí)不在于技術(shù)上,而是商業(yè)模式上,回到文章開頭的第一個(gè)觀點(diǎn),半導(dǎo)體這個(gè)行業(yè),很多時(shí)候不是技術(shù)導(dǎo)向,而是商業(yè)導(dǎo)向...做EMIB,同時(shí)需要對(duì)硅和基板有深入加工的能力,而英特爾是個(gè)IDM,它有fab和封裝線,天然適合這么做,甚至英特爾可能比基板企業(yè)更了解基板材料和性質(zhì)畢竟,ABF的一切幾乎都是它定義的,而事實(shí)上,英特爾為了EMIB,開發(fā)了特殊的加成法基板制備工藝和硅橋嵌埋在基板上的特殊面板級(jí)封裝工藝,貼裝的DAF材料和電鍍藥水也是定制的,這種折騰程度只有IDM玩得轉(zhuǎn)。而對(duì)于臺(tái)積電來(lái)說(shuō),它能力在硅上,它不想也不希望動(dòng)基板,基板良率又低價(jià)格又高,為什么我不安心搞我的2.5D中介層?甚至臺(tái)積電連硅橋也不想做,因?yàn)楣铇騼r(jià)格比一整塊中介層低太多 了(你們這幫芯片企業(yè)又想用上HBM和大面積MCM, 又不想買我800m㎡+的中介層!),對(duì)于用了硅中介層的芯片,臺(tái)積電也只做到封好芯片+中介層,中介層貼裝到基板上的步驟交給別的OSAT…而日月光等OSAT,缺乏做硅橋和中介層的能力,它們也不是很想碰這些東西,所以他們主推的是高密度RDL互聯(lián)或者直接wafer to wafer鍵合。但是對(duì)于芯片設(shè)計(jì)公司來(lái)說(shuō),他們很希望有一個(gè)比硅中介層便宜,性能比傳統(tǒng)RDL互聯(lián)好的方案出現(xiàn),他們也渴望自己不會(huì)被綁定在某一家封裝廠或者載板廠上,這個(gè)需求又推進(jìn)業(yè)界開發(fā)一個(gè)對(duì)標(biāo)EMIB的硅橋技術(shù)。

硅橋自身也是要對(duì)外互聯(lián)的,以前只有英特爾特制的ABF基板能滿足硅橋?qū)ν饣ヂ?lián)的布線需求,但是你要fab和OSAT玩這個(gè)不是為難人家嗎?于是,有人想到用扇出封裝里的RDL層代替基板,包覆住硅橋(這就是為啥EFB會(huì)高出一層,這層是基板代餐),可惜早期的晶圓級(jí)扇出封裝的RDL不足以承擔(dān)這個(gè)密度的布線,直到后來(lái)業(yè)界迎來(lái)了高密度RDL技術(shù)的突破(于是今年一下子AMD和蘋果都上了),高密度的RDL使用了前道半導(dǎo)體級(jí)別的工藝,精度非常高,可以實(shí)現(xiàn)2微米線寬,一下子在技術(shù)指標(biāo)上拉到和EMIB一個(gè)水平,而且成品是兼容標(biāo)準(zhǔn)FC工藝的!(這點(diǎn)很重要)。

小故事一則(復(fù)讀我以前的微博):當(dāng)年Fury顯卡領(lǐng)先業(yè)界用上了HBM顯 存,但是一直缺貨,官方說(shuō)法是HMB良率不行,這里有一個(gè)另一個(gè)版本的故事,Fury是業(yè)界最早用上 2.5D封裝的顯卡,AMD覺得核心和硅中介層不要都放在臺(tái)積電做,臺(tái)積電開價(jià)太狠了,于是找來(lái)了別的OSAT,OSAT說(shuō)硅中介層我搞不定,于是AMD又拉來(lái)了聯(lián)電,聯(lián)電很開心,不光幫助設(shè)計(jì)了硅中介層甚至排了產(chǎn)能專門做硅中介層,然而等到量產(chǎn)的時(shí)候臺(tái)積電,聯(lián)電,OSAT,AMD四方終極拉扯...互相指責(zé)對(duì)方環(huán)節(jié)有問題,于是Fury就這樣在拉扯中度過了一生從此以后,AMD還是決定在臺(tái)積電把芯片+中介層做完封裝完再拿出去找OSAT,但是,資本家怎么會(huì)讓別人一直賺自己的錢呢?現(xiàn)在出現(xiàn)的EFB是一個(gè)兼容標(biāo)準(zhǔn)FC工藝的封裝技術(shù),硅橋、RDL層合封、貼裝在基板上等工序都可以找不同的廠商來(lái)做,AMD依然沒有放棄它的”靈活供應(yīng)鏈“之旅,利益最大化沒毛病,這行業(yè)都是這樣打算盤的。

4.區(qū)分InFO與CoWoS

在蘋果M1Ultra發(fā)布之后,國(guó)內(nèi)媒體都在傳一個(gè)臺(tái)媒新聞,M1U使用了臺(tái)積電CoWoS-S,我當(dāng)時(shí)看了發(fā)布會(huì)上關(guān)于互聯(lián)的演示,和朋友吐槽這絕對(duì)不可能是CoWoS-S,要么CoWoS-L要么InFO-LSI,還發(fā)了微博,后來(lái)臺(tái)積電證實(shí)了M1U使用的是InFO-LSI,那么如何區(qū)分InFO與CoWoS?

由于有載板類的InFO封裝的出現(xiàn),InFO不再像以往只能封裝一些面積小的芯片,封裝尺寸可以比肩甚至超過CoWoS,而CoWoS本身也分為S、R、LSI三種,一般我們提到CoWoS,默認(rèn)就是在說(shuō)CoWoS-S,也就是所有芯片被承載在一層硅轉(zhuǎn)接板上,這是最經(jīng)典也是性能最好最常見的CoWoS,缺點(diǎn)就是成本很高,一般來(lái)說(shuō),當(dāng)一個(gè)芯片用了硅橋而非整塊的硅片,基本上可以確認(rèn)是使用了InFO-LSI或者FoCoS-LSI等類似的工藝,CoWoS實(shí)際上也有一個(gè)R(用高密度RDL代替硅轉(zhuǎn)接板,對(duì)位高密度的FoCoS),一個(gè)L(硅橋+RDL版本),這兩個(gè)和InFO-oS、InFO-LSI看起來(lái)形式上是一樣的,甚至參數(shù)上都重疊了,除非廠商自己回答或者開盒檢測(cè),不然是幾乎無(wú)法通過紙面數(shù)據(jù)區(qū)別。

這兩類東西在生產(chǎn)流程上倒是比較好區(qū)分開來(lái),RL在流程上和CoWoS-S類似,即中介層是可以單獨(dú)生產(chǎn)出來(lái)交給客戶的,客戶可以拿著中介層配上die找別人封裝的,而InFO-oS和LSI則基本上不存在獨(dú)立中介層一說(shuō),它的中介層也就是RDL層是扇出封裝的一部分,交到客戶手上一定是包含了芯片的一個(gè)整體,當(dāng)然客戶可以把這個(gè)整體拿去繼續(xù)找別人做進(jìn)一步封裝,比如pop堆疊一個(gè)內(nèi)存或者貼裝在基板上。

5.關(guān)于M1U的雜談

M1U發(fā)布以后,不知道誰(shuí)先提出了的,M1U是一對(duì)M1Max不切割直接從晶圓上直接切下來(lái)的

其實(shí)這個(gè)謠言想一下就知道靠不住,首先果子為啥用先進(jìn)封裝,不就是封裝技術(shù)演進(jìn)到足夠互聯(lián)多個(gè)高性能SoC所以不用再制造單顆大SoC了嗎,結(jié)果它又跑回去找一對(duì)面對(duì)面完好的M1MAX去做整切芯片了?這不是搬起晶圓砸自己的腳嗎?其次,如果是一對(duì)整切,那實(shí)際上下半個(gè)M1MAX是要被翻轉(zhuǎn)過來(lái)的,在量產(chǎn)中是沒有人會(huì)這么干,像藍(lán)寶石激流,看起來(lái)是4個(gè)一樣的die,實(shí)際上是兩種在不同晶圓上互為鏡像的die。(還有如果一邊M1MAX有瑕疵要屏蔽部分單元,那對(duì)面的M1MAX是不是也不得不屏蔽幾個(gè)給你湊湊?樂

)

這時(shí)候就有人會(huì)說(shuō),不是很多大V都說(shuō)蘋果專利里面就是整切的啊,首先,702A1那個(gè)專利本質(zhì)是寫一種直接在BOEL上通過build-up做互連層的專利,可以不需要引入硅橋,不需要TSV就直接與周圍的die形成互聯(lián),其實(shí)與目前的M1U關(guān)系不大。當(dāng)然這個(gè)專利也說(shuō)明了,如果die和周圍的die互聯(lián)沒問題,可以考慮整切,這個(gè)玩意根據(jù)果子專利里給的圖,每個(gè)die有等邊的IO互聯(lián)部分,整切出4連芯片,至于未來(lái)會(huì)不會(huì)見到這種技術(shù),不好說(shuō),回到文章開頭的第一個(gè)觀點(diǎn),看成本看商業(yè),有興趣可以借助晶圓良率計(jì)算器算算,要4個(gè)沒問題或者品質(zhì)一致的die整切,是不是個(gè)容易的事。

真正關(guān)于蘋果目前商用的封裝技術(shù),應(yīng)該是在504A1里,幾乎就快把硅橋兩字寫在臉上了

另外這份專利可以看出果子在材料上也下了很大很大的功夫,有興趣直接去搜這份專利吧~

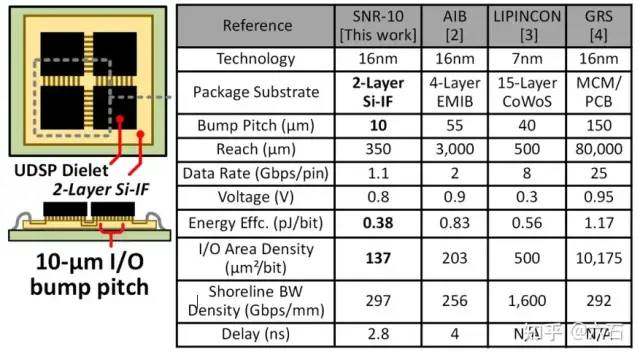

6.Si-IF技術(shù)

夾帶一個(gè)私貨

,Si-IF互聯(lián),在ISSCC2022論文里看到的一個(gè)挺有意思的”2.5D封裝方式“,

Si-IF似乎是一種嵌埋式的“硅線?”,只需要兩層,能夠?qū)崿F(xiàn)100um距離的高速通訊,基本上各方面都優(yōu)于傳統(tǒng)的板級(jí)MCM,占地面積和能耗比超過目前所有互聯(lián)方案(雖然單位面積的速度不高),挺好奇這個(gè)Si-IF后續(xù)會(huì)不會(huì)被推廣,是一個(gè)比板級(jí)MCM走線好不少的方案,目前我也不知道這個(gè)Si-IF的制作工藝和是哪家廠在推進(jìn)的,但是一旦碰到了基板中的嵌埋,事情就會(huì)復(fù)雜起來(lái)

。順便上圖這個(gè)表里也說(shuō)明了一個(gè)問題,板級(jí)MCM沒有那么不堪,在不少關(guān)鍵數(shù)據(jù)上是不比表里早期的EMIB差多少的,這也說(shuō)明了為啥ZEN系列和英特爾自己的合封了一個(gè)I/O die的筆記本處理器為啥不用硅橋技術(shù)了(當(dāng)然是太貴了)。

三.3D先進(jìn)封裝

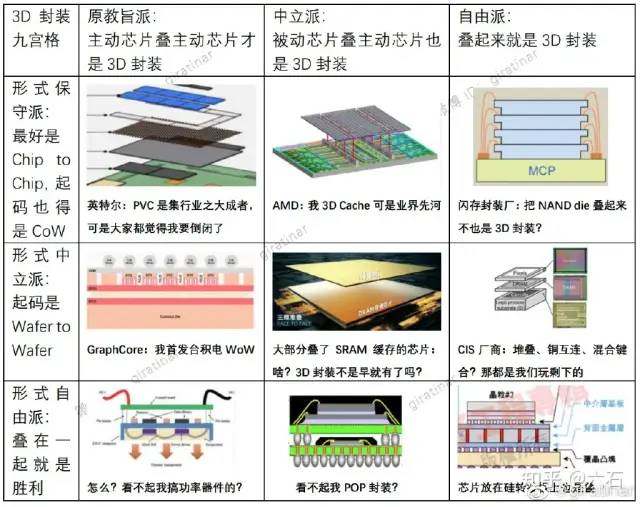

1.定義與限制條件(排除MEMS和CIS)

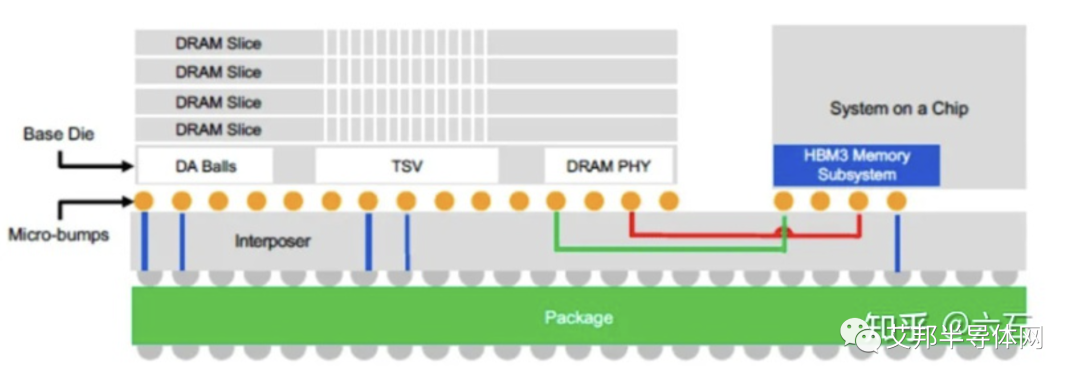

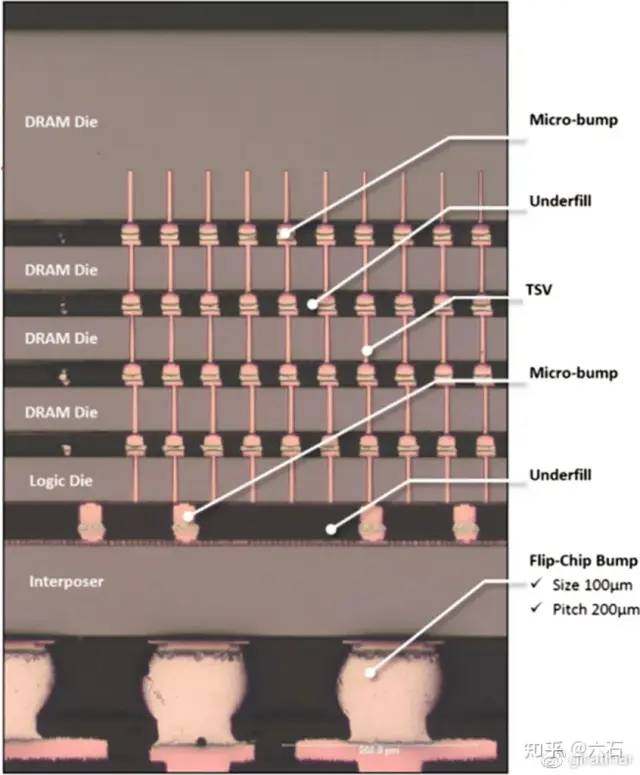

在說(shuō)3D封裝之前,有必要說(shuō)說(shuō)3D封裝到底是啥,就如同上圖所示一樣,如果只是以簡(jiǎn)單的兩個(gè)東西堆疊來(lái)定義3D封裝的話,那3D封裝有很多很多,也早就被應(yīng)用在各個(gè)領(lǐng)域了(比如POP封裝,現(xiàn)在的手機(jī)芯片基本都是SoC上堆疊了一個(gè)DRAM,比如NAND顆粒里的堆疊)。所以狹義的3D封裝是排除了這類”簡(jiǎn)單“堆疊的封裝,它一般是指,在一個(gè)封裝體(比如一個(gè)molding里、一個(gè)金屬頂蓋下)兩顆die在垂直方向上直接互聯(lián)的封裝(POP封裝下,DRAM與下方的SoC并沒有直接互聯(lián))。而這兩個(gè)die,一般來(lái)說(shuō)是被動(dòng)芯片(一般是各類存儲(chǔ))疊在主動(dòng)芯片上(計(jì)算芯片、BASE Die、I/O Die等等),比如5800XD,或者主動(dòng)疊在主動(dòng)上(主動(dòng)疊在被動(dòng)上那就是2.5D封裝了),比如LakeField。

目前見的比較多的是被動(dòng)疊主動(dòng),業(yè)務(wù)已經(jīng)有不少疊了SRAM的AI芯片出現(xiàn),還有5800XD這種消費(fèi)類的產(chǎn)品,這種3D封裝形式常見的原因也很簡(jiǎn)單,因?yàn)樵O(shè)計(jì)上冗余程度更大,主動(dòng)芯片的設(shè)計(jì)也更自由,下方的主動(dòng)芯片本質(zhì)上還是一個(gè)普通的SoC/chiplet,上方的被動(dòng)芯片一般是一塊SRAM,而主動(dòng)疊主動(dòng)則是把一個(gè)SoC拆成不同部分再堆疊起來(lái),得考慮不同部分之間得互聯(lián)還有散熱問題,尤其是后者,幾乎是現(xiàn)在主動(dòng)疊主動(dòng)的死穴,英特爾遲遲不在3D封裝上用混合鍵合也是有這方面的考慮。

至于3D封裝缺陷嗎,這里不多介紹了,應(yīng)該是人都想得到吧,發(fā)熱、貴、設(shè)計(jì)復(fù)雜、電磁干擾嚴(yán)重、熱應(yīng)力、結(jié)構(gòu)。。。。。

然后CIS和MEMS上的3D封裝,下文就不討論了,我也不太了解,CIS封裝幫助行業(yè)試水和量產(chǎn)了很多關(guān)鍵技術(shù),比如TSV、混合鍵合、CU直連、RW等等,做CIS封裝的OSAT不少都有能力去做數(shù)字芯片領(lǐng)域的先進(jìn)封裝。還有射頻、光電領(lǐng)域的先進(jìn)封裝這里也不討論了,以后有機(jī)會(huì)另說(shuō)。

定義完3D封裝,下面就介紹一下3D封裝幾個(gè)關(guān)鍵技術(shù),一個(gè)是TSV,一個(gè)是混合鍵合。

2.關(guān)于3D Cache的誤會(huì)(一部分搬運(yùn)一下以前的回答)

在聊TSV和混合鍵合之前,先扯幾句AMD的5800XD上的3D Cache,也算作為一個(gè)引子吧,在3D Cache技術(shù)公布之后,包括linus、Anandtech、AMD油管官方平臺(tái)、很多知乎和微信文章里,都把3D Cache的成功歸結(jié)于TSV對(duì)比ubump的優(yōu)勢(shì),對(duì)真正的核心點(diǎn)混合鍵合幾乎無(wú)視,這其實(shí)讓人很摸不著頭腦(semiwiki就沒有,而是直接點(diǎn)出了關(guān)鍵點(diǎn)在混合鍵合)

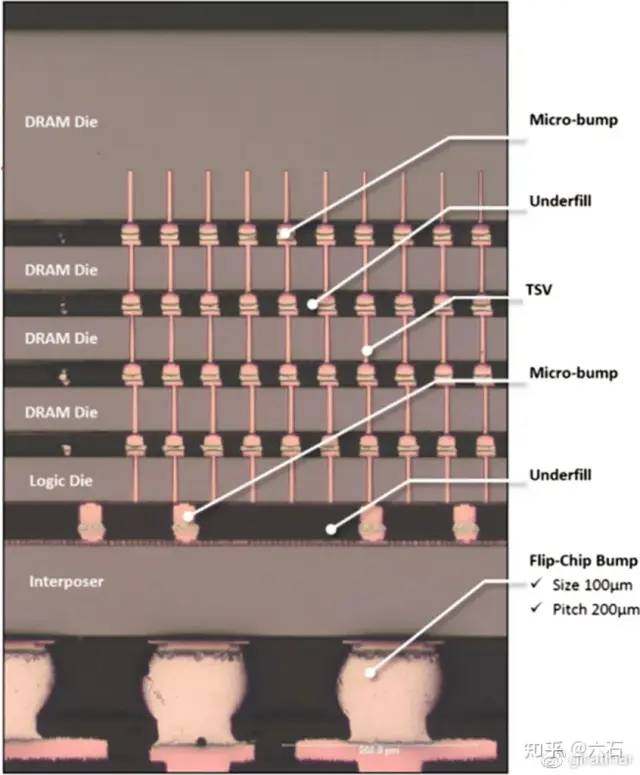

TSV在芯片內(nèi)部的,作用是垂直方向傳輸信號(hào),而且兩個(gè)芯片垂直方向上3D物理互聯(lián)是用不了TSV的…和TSV無(wú)關(guān)……因?yàn)檫@個(gè)已經(jīng)在芯片外部了…ubump/混合鍵合/cu-cu互聯(lián)/微銅柱這些和TSV不一樣,這是兩個(gè)東西,TSV/TDV/TGV都是芯片或者介質(zhì)里做通孔,像在芯片里面建電梯一樣,打通數(shù)據(jù)在垂直方向的傳輸,ubmp/混合鍵合這些是兩個(gè)芯片垂直方向物理上的直接粘合/鍵合(當(dāng)然它們也可以傳數(shù)據(jù)和供電) ,所以那些文章說(shuō)3D cache比英特爾3D互聯(lián)封裝強(qiáng)的原因是因?yàn)槭褂肨SV而不是ubump真的讓人摸不著頭腦,何況英特爾3D封裝里有TSV。。。

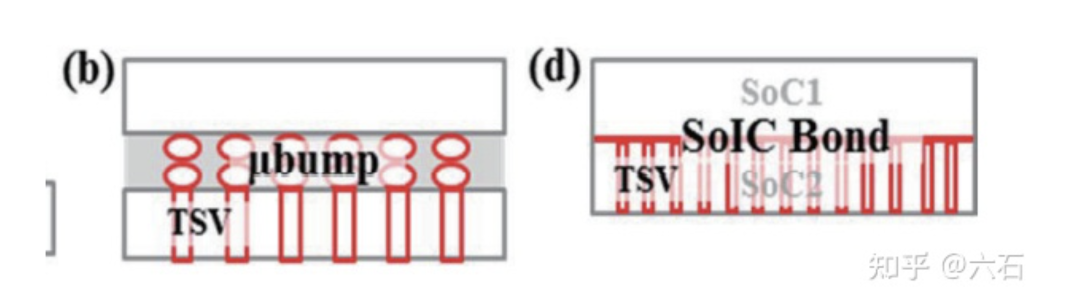

目前現(xiàn)有的3D主要有兩種,一種是F2F(即晶體管、信號(hào)層所在那層面對(duì)面互聯(lián)) ,因?yàn)樾盘?hào)層貼臉了,所以不需要TSV,使用晶圓級(jí)的混合鍵合就可以了,這類封裝國(guó)內(nèi)的武漢新芯做的很不錯(cuò)。另一種是F2B(B就是芯片的背面,那里只有沒有實(shí)際作用的硅),這種一般是芯片對(duì)芯片/晶圓鍵合(c2c/c2w),由于底下的芯片自身是倒裝貼裝基板上的,所以需要使用TSV,一般是ubump+TSV,典型是英特爾現(xiàn)在的3D封裝。ubump的IO密度是低于混合鍵合的,但是在芯片對(duì)芯片/晶圓的3D封裝上,使用混合鍵合是很難對(duì)準(zhǔn)的,所以一般得退而求其次使用ubump。而AMD這次展示的3D封裝,是混合鍵合+TSV的,沒有使用ubump(所以通稿還懟了英特爾一下哈哈),而且更狠的在于臺(tái)積電現(xiàn)在這個(gè)3D封裝在提供比英特爾等廠商現(xiàn)有3D封裝厚度更低,I/O密度更高的性能指標(biāo)下,還允許封裝上層芯片面積自由選擇,不需要和下方芯片面積一樣!(傳統(tǒng)的晶圓級(jí)鍵合沒有這么自由,而在5800XD上我們可以看到AMD并不需要和CCD一樣大的緩存芯片),我還記得和某做服務(wù)器芯片外包封裝設(shè)計(jì)的人提到這個(gè)事的時(shí)候,他的第一反映是這是不可能的

除非臺(tái)積電找設(shè)備廠定制了一套新方法,事實(shí)上,在3D cache技術(shù)亮相的那個(gè)時(shí)間節(jié)點(diǎn)附近,確實(shí)可以看到一則應(yīng)用材料與合作伙伴在混合鍵合上取得重大突破的新聞。

3.關(guān)鍵技術(shù)——令人痛恨的TSV

本來(lái)還想多寫一些TSV,但是發(fā)現(xiàn)有篇很好的文章可以看看,《TSV簡(jiǎn)史》一些內(nèi)容我就不再寫了,大佬寫的比我好多了。TSV從誕生之初到現(xiàn)在,業(yè)界其實(shí)一直在頭疼他的良率、它的填孔好壞怎么解決,作為先進(jìn)封裝至關(guān)重要的組成部分,TSV一直是令人又愛又恨的東西。

可能有人會(huì)說(shuō),我看我家鄉(xiāng)那里,某某小封裝廠說(shuō)自己的TSV工藝很成熟,怎么會(huì)難做,其實(shí)TSV也封好多種,很多封裝廠口中的TSV,其實(shí)是一種梯形的斜孔,深寬比較低,一般只到芯片的信號(hào)互聯(lián)層,難度自然也低。而穿過整個(gè)芯片,實(shí)現(xiàn)上下完全互通的TSV是一種深寬比較高的通孔,會(huì)直接侵入晶體管所在的位置,它的難度大,良率低。

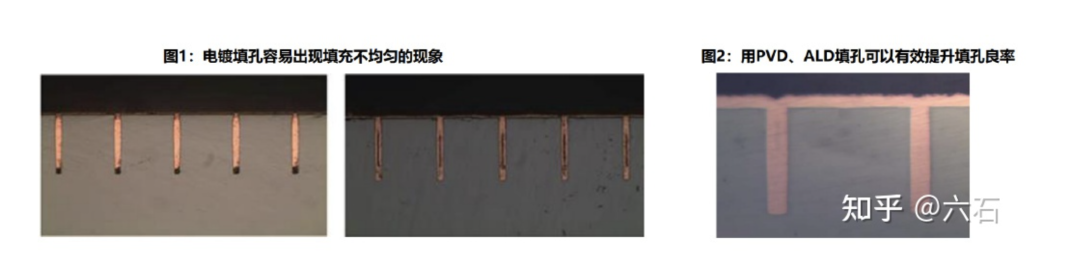

更麻煩的在于,TSV如何更好更快的填充?傳統(tǒng)的TSV都是使用電鍍法,但是電鍍法填充容易出現(xiàn)有空穴、孔壁有毛刺不夠光滑等問題,尤其是在先進(jìn)封裝使用的深孔填充中,這是一個(gè)令人頭疼的問題,除了良率更低以外,因?yàn)橼吥w效應(yīng)的存在,填充的不夠好的通孔在傳輸高頻高速信號(hào)會(huì)嚴(yán)重的損耗,使得芯片達(dá)不到預(yù)期的性能。目前業(yè)界已經(jīng)開始嘗試使用PVD甚至ALD來(lái)填充TSV(這兩者本身就是TSV沉積絕緣層和種子層的常用設(shè)備),但是成本和速率還遠(yuǎn)遠(yuǎn)比不上電鍍法,未來(lái)TSV填孔如何解決只能交給時(shí)間來(lái)回答了。

4.關(guān)鍵技術(shù)——混合鍵合

我還記得我2020年見到英特爾封裝研究院前材料首席研究員(發(fā)明了喜聞樂見的CPU上的釬焊、各類bump、EMIB材料、Fovers封裝的材料)的時(shí)候,她信誓旦旦的和我說(shuō),混合鍵合問題很多,解決不了發(fā)熱和信號(hào)傳輸問題,英特爾不會(huì)用的!在當(dāng)時(shí)Fovers還是用ubump實(shí)現(xiàn)了主動(dòng)芯片上堆疊主動(dòng)芯片,雖然是lakefield

,后來(lái)的GPU PVC也是。混合鍵合還只是在主動(dòng)疊被動(dòng)以及傳感器上使用,甚至如今AMD的5800XD也是如此,(GraphCore的那顆用了臺(tái)積電WoW3D封裝芯片我仔細(xì)看了一下,下方的die是專門做供電的,嚴(yán)格來(lái)說(shuō)不太能算主動(dòng)疊主動(dòng))直到英特爾后來(lái)自己畫了餅,說(shuō)Fovers下一代Fovers-direct將會(huì)使用混合鍵合

我一時(shí)感到有點(diǎn)語(yǔ)塞,所以英特爾找到了方法用混合鍵合實(shí)現(xiàn)主動(dòng)芯片疊主動(dòng)芯片?我想大概率和那個(gè)ODI技術(shù)有關(guān)系,用大銅柱輔助散熱和供電,也不知道14代處理器會(huì)不會(huì)用上混合鍵合。

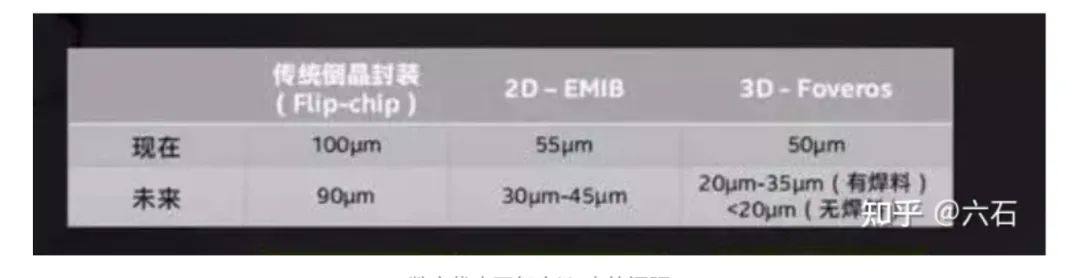

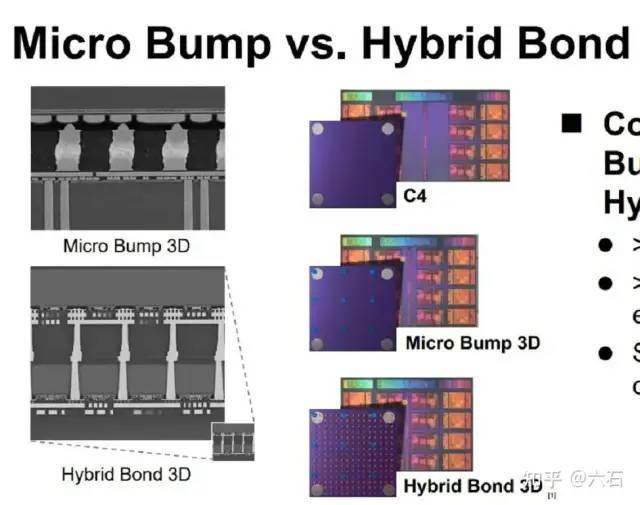

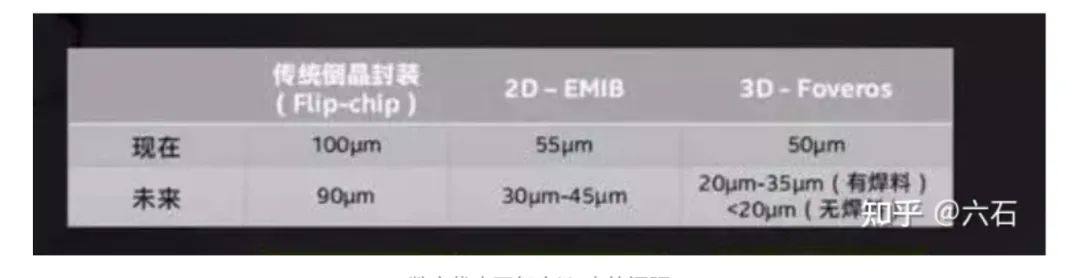

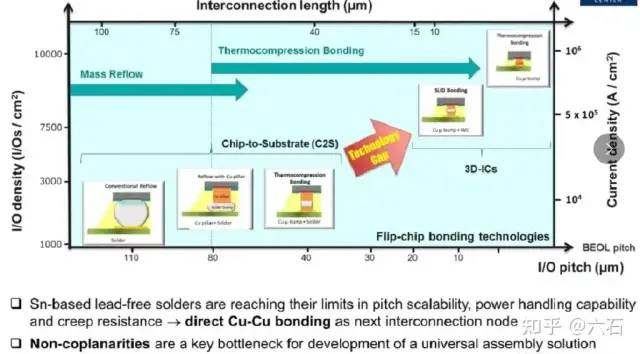

好了瞎扯完了,正經(jīng)聊一下混合鍵合,混合鍵合這個(gè)技術(shù)逐步流行的原因很簡(jiǎn)單,如文章開頭第二個(gè)觀點(diǎn)所說(shuō),封裝演進(jìn)本質(zhì)是提升I/O密度的提升,像上圖一樣,傳統(tǒng)的FC每個(gè)焊點(diǎn)之間的間距只能到90微米,可以簡(jiǎn)單理解為間距越大,IO密度越低。EMIB努力努力,能達(dá)到30-45微米,和CoWoS到一個(gè)水平線上,3D-Foveros使用比C4還要小的ubump,間距在25微米左右,和InFO-LSI一致。

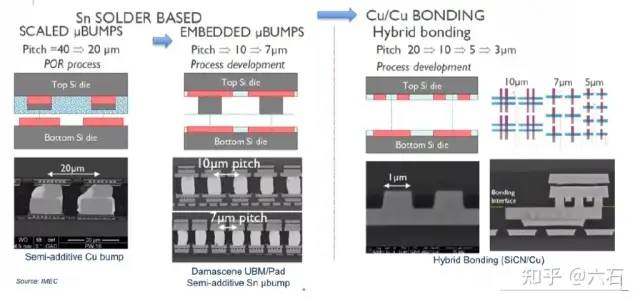

但是再往下,受制于原理,本身就是一個(gè)球的bump已經(jīng)很難再縮小間距了(辦法也有),于是以微銅柱為核心的混合鍵合就逐步走入先進(jìn)封裝領(lǐng)域。一般我們說(shuō)混合鍵合,都是指銅混合鍵合,早在2005 年,一個(gè)叫Ziptronix的公司就推出了一種稱為低溫直接鍵合互連 (DBI) 的技術(shù),后來(lái)這個(gè)技術(shù)被索尼買去了,用在CIS的模擬層和數(shù)字層堆疊上,這項(xiàng)技術(shù)也因此現(xiàn)在CIS領(lǐng)域普及開來(lái),使得很多封裝廠都有做晶圓級(jí)鍵合的能力。

bump本身是有是由局限性的,傳統(tǒng)的bump只能把間距縮小到20微米,再改變材料,復(fù)用類似工藝流程,并借助TCB(后文會(huì)說(shuō))的情況下,也只能到7微米了,但是別忘了ubump本身還不小(直徑5微米是目前最秀水平了),所以實(shí)際IO密度會(huì)更低。而混合鍵合可以縮小到3微米,本身尺寸可以做到1微米,這對(duì)于bump來(lái)說(shuō),幾乎是碾壓的。

但是同樣的,混合鍵合也有很多麻煩,混合鍵合用于晶圓到晶圓w2w和芯片到晶圓c2w的鍵合。混合鍵合工藝一樣也很復(fù)雜所需的芯片在晶圓廠的兩個(gè)晶圓上進(jìn)行處理,將需要的介電材料沉積在晶圓的一側(cè),然后為晶圓上的每個(gè)芯片在對(duì)應(yīng)的沉積層上通孔。再將銅材料沉積上去。然后,化學(xué)機(jī)械拋光 (CMP) 工具拋光表面,把多余的銅抹去,剩下的是每個(gè)芯片的微小通孔中的銅金屬化材料(與TSV異曲同工了),然后再經(jīng)過檢查、進(jìn)一步的CMP,最后才是使用晶圓鍵合機(jī),將其堆疊并鍵合到第二個(gè)晶圓上。

然而在鍵合的過程中,精度也是一個(gè)非常令人頭疼的東西,尤其是c2c/c2w這類的鍵合,一旦上下兩個(gè)die面積不一樣(像5800XD),這難度還要成倍增加,另外鍵合的時(shí)候是需要“高溫”讓銅融化連在一起的這里面又會(huì)有很多幺蛾子,比如晶圓翹曲、鍵合過程中開裂,還有很多奇妙know-how:大家都知道熱脹冷縮,所以像上圖右下方的圖示一樣,黃色的銅會(huì)被減少一些,讓它在受熱過程中膨脹正好完成互聯(lián),但當(dāng)這個(gè)銅柱縮到足夠小的時(shí)候,反而要讓銅多出來(lái)一些。。。。

總之,鍵合也不是一個(gè)善茬,但是讓英特爾和很多以倒裝為主的封裝廠一直“抵觸”鍵合的原因還有一個(gè),混合鍵合所需要的設(shè)備和倒裝基本不一樣,相當(dāng)于他們之前投的設(shè)備是不能用的,工藝積累也是白費(fèi)的,反而像臺(tái)積電這種它沒有歷史包袱,這又回到文章的第一個(gè)觀點(diǎn)了,每個(gè)企業(yè)自身的商業(yè)模式和利益考量,也會(huì)影響它們的技術(shù)選擇。下面就讓我們來(lái)聊聊,大怨種英特爾和它的TCB

5.英特爾和他的TCB

前面我們提到,混合鍵合的設(shè)備與原本兼容倒裝和bump的設(shè)備是完全不同的,這對(duì)于IDM的英特爾和很多封裝廠來(lái)說(shuō)是很不友好的(資本家:又要掏錢買設(shè)備?以前的為什么不能用?)英特爾是因?yàn)榛舜箦X買了很多TCB設(shè)備,而對(duì)于大多數(shù)OSAT來(lái)說(shuō),這項(xiàng)技術(shù)成本過高,需要昂貴的半導(dǎo)體晶圓設(shè)備來(lái)實(shí)現(xiàn)這些工藝,反而是UMC、臺(tái)積電對(duì)混合鍵合很積極,它們可以復(fù)用自己的半導(dǎo)體晶圓級(jí)設(shè)備。

而bump再往下走通過改進(jìn)材料(從錫球變成銅塊)和工藝,是能把間距做到10微米以內(nèi)的,這種bump現(xiàn)在一般叫做微凸塊,而這種微凸塊在大部分工藝流程和設(shè)備上與原本的bump是類似的(起碼是一個(gè)技能樹上的)英特爾封裝開發(fā)工程師Zhaozhi Li在去年的ECTC大會(huì)上表示。“在保持與現(xiàn)有硅和封裝技術(shù)兼容的同時(shí),利用現(xiàn)有的基礎(chǔ)設(shè)施,將焊料微凸點(diǎn)互連微縮至更小的間距可能仍然是有利的。”他這個(gè)話,代表了大部分OSAT和英特爾自身的想法,即盡量兼容原有工藝,然后使用的一種名為TCB(熱壓鍵合)的技術(shù)實(shí)現(xiàn)10微米間距以內(nèi)的微凸塊貼裝用以滿足先進(jìn)封裝需求,而不是直接上混合鍵合。(還有個(gè)技術(shù)路徑是LAB,是安靠和長(zhǎng)電主推,這里不談了)

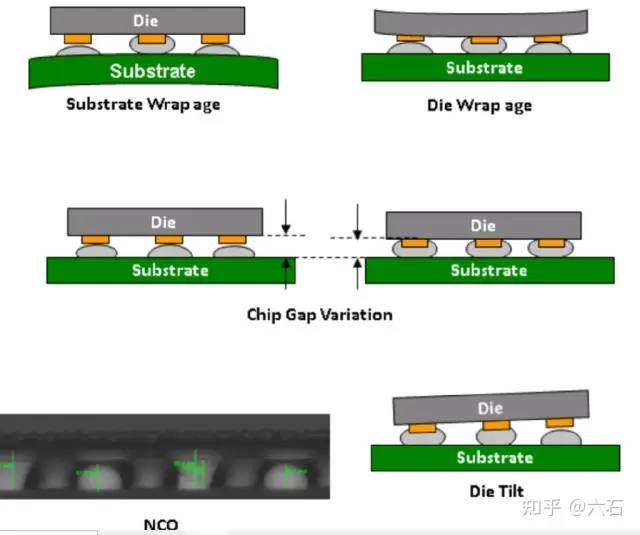

倒裝血壓升高合集

TCB 工藝有什么特殊之處?在這之前我們先看看傳統(tǒng)的倒裝,標(biāo)準(zhǔn)倒裝芯片會(huì)被芯片放置工具將放置在基板、中介層或載體上,一次放置是上百甚至上千個(gè)。然后將放置好的模具組進(jìn)入回流爐,這數(shù)百個(gè)甚至數(shù)千個(gè)封裝放入烤箱中,加熱到使焊料熔化的溫度以完成粘合,然后繼續(xù)批量進(jìn)行后續(xù)步驟,這個(gè)過程很快效率也很高,但是由于回流爐中加熱會(huì)導(dǎo)致芯片、基板、焊球以不同的速率膨脹,從而發(fā)生翹曲導(dǎo)致芯片不能很好的被粘合,最后導(dǎo)致良率出現(xiàn)問題。而隨著bump本身在變小,間距在縮小,這個(gè)問題也越發(fā)困擾廠商,像早期2.5D封裝的芯片普遍都遇到了良率問題就是因?yàn)榈寡b本身不夠”精細(xì)“。隨著bump逐步走到10微米以下,傳統(tǒng)這種批量加工的方式顯然已經(jīng)不適合了,bump尺寸的減少轉(zhuǎn)化為更小的錯(cuò)誤余量,因此TCB應(yīng)運(yùn)而生。

TCB(熱壓粘合/鍵合)工藝中,不再有把大量芯片批量運(yùn)送到回流爐這一步了,而是使用單一工具放置單個(gè)芯片,直接對(duì)這個(gè)芯片施加壓力并加熱它們以回流粘合焊球。這種方式從芯片頂部加熱(因?yàn)楸举|(zhì)還是倒裝,所以加熱的那面是沒有晶體管的硅),因此只有芯片和bump焊接連接處會(huì)發(fā)熱。這就避免了下方基板翹曲問題,而且由于是單一放置且主動(dòng)施力,可以確保均勻粘合,沒有間隙變化或傾斜。同時(shí)TCB設(shè)備在粘合時(shí)候還會(huì)伴隨著快速振動(dòng),破壞銅焊盤和焊球上的金屬氧化。也因此TCB在相同的bump間距下能實(shí)現(xiàn)更好的電氣特性,也允許bump間距縮放到更小的尺寸,這種方式也適合對(duì)非常薄的芯片進(jìn)行堆疊封裝,這是HBM普遍使用TCB的原因(HBM廠商也在研究混合鍵合的辦法),與標(biāo)準(zhǔn)倒裝芯片工藝流程相比,TCB似乎是一種完全更好的技術(shù),除了回流部分以外基本和倒裝一致,為啥TCB實(shí)際上除了英特爾之外用的廠商不算多呢?當(dāng)然是成本和商業(yè)模式的問題啦~

TCB每小時(shí)能處理的die數(shù)量只有傳統(tǒng)倒裝設(shè)備的三分之一甚至更低,成本卻接近后者的三倍,這對(duì)OSAT廠商來(lái)說(shuō)是一個(gè)巨大的壞消息,本身OSAT廠商毛利就不高,還要用上這種花錢工藝,在技術(shù)還沒成熟、客戶接受度不高的時(shí)期,這種降低毛利的辦法真是令人難受,而且OSAT目前買TCB一般用于移動(dòng)端等小面積、相對(duì)低功耗的處理器,這種應(yīng)用的毛利實(shí)在沒法和大芯片比,但是資本家為了不買全新的混合鍵合產(chǎn)線,還是咬牙接受了。

那么,那地球上有誰(shuí)能肆無(wú)忌憚的上TCB呢?那當(dāng)然是,我們,天天被人認(rèn)為 的英特爾啦,英特爾擁有近 300 種 TCB 工具,遠(yuǎn)超過了英特爾的先進(jìn)封裝的需求,以至于英特爾在許多非高級(jí)封裝應(yīng)用中使用 TCB

,SemiAnalysis給出的理由很有趣,因?yàn)橛⑻貭栐诟吖β屎透呃麧?rùn)應(yīng)用中占有很大份額,產(chǎn)量損失和可靠性問題遠(yuǎn)遠(yuǎn)超過了每單位封裝工具的微不足道的攤銷成本。這大概就是,毛利高的IDM的底氣吧,地主家的余糧還是很多的

而且借助TCB,英特爾可以對(duì)自家的標(biāo)準(zhǔn)封裝、2.5D 封裝和3D封裝使用相同的工具,前提是這些die使用的都是bump技術(shù)

這也解釋了為什么,混合鍵合對(duì)bump幾乎是降維打擊,但是英特爾在混合鍵合上的動(dòng)作卻緩慢了,英特爾在TCB上積累十多年,投入了大量財(cái)力和研究,把bump上限拉到了混合鍵合的水平,不可能就棄之不用,而且對(duì)于英特爾來(lái)說(shuō),TCB的工藝更成熟,不需要新的投入,設(shè)備折舊也快做完了,對(duì)于毛利率來(lái)說(shuō)是一個(gè)好事。還是文章開頭的那個(gè)觀點(diǎn),這個(gè)行業(yè)都是要賺錢的,商業(yè)有時(shí)比技術(shù)更重要。

PS:另外某為和日月光在TCB上合作蠻深的,2020年年底還有謠傳日月光在大陸給某為建設(shè)了封裝廠,然后在2021年年底,日月光在行業(yè)景氣度還很不錯(cuò)的情況下賣給智路資本4家工廠,結(jié)合智路資本以往的操作和后臺(tái),很難不聯(lián)想呀

四.未來(lái)(這部分不少是推測(cè)!看看圖個(gè)樂就好)

1.臺(tái)積電的野望

前面我們一直在強(qiáng)調(diào),成本、商業(yè)模式?jīng)Q定了很多這個(gè)行業(yè)很多的抉擇與方向,TSV是一個(gè)3D封裝領(lǐng)域幾乎離不開的技術(shù),一般來(lái)說(shuō)狹義上的TSV是一種”后道“工藝,即它是在芯片做完之后,再做開孔、填孔,也就是說(shuō),芯片制造和TSV產(chǎn)生并不需要在一個(gè)公司手里

,而且目前這種方式制作的TSV還有上文說(shuō)的這么多問題,你看啊,3D先進(jìn)封裝未來(lái)算是一個(gè)大肥肉,TSV問題這么多,我臺(tái)積電有沒有一種辦法,解決了TSV的問題,這樣大家就離不開我啦

當(dāng)然有的,前面我們提到,TSV也分為在芯片上和在中介層上兩種,在芯片內(nèi)部做TSV的破壞性是很大的,需要芯片制作完成后再打孔。而臺(tái)積電準(zhǔn)備了一種”TSV-less“技術(shù),”TSV-less“本質(zhì)還是一種TSV,只是從”后道“變成”前道“工藝,有了解過3D NAND制備工藝的人應(yīng)該知道在3D NAND的生產(chǎn)過程中,就會(huì)制造出從頂層到底層的深孔,然后用ALD、PVD等技術(shù)把這些深孔填充,起到的作用和TSV基本一樣(其實(shí)他們這個(gè)也是一種TSV),但是不需要像狹義的TSV那樣在完成制造之后再對(duì)晶圓做破壞性的操作。臺(tái)積電的”TSV-Less“原理也是類似,在芯片光刻的過程中就把”TSV“給做出來(lái),借助ALD、PVD這類沉積精度非常高的技術(shù),可以沉積出孔壁光滑,深寬比大的通孔,這代來(lái)的優(yōu)勢(shì)是狹義上的后道TSV無(wú)法追上的。

這樣子除了在技術(shù)上有優(yōu)勢(shì),在商業(yè)上也很有好處,相當(dāng)于客戶對(duì)于臺(tái)積電的依賴更深了,而且這個(gè)技術(shù)和F2F的晶圓鍵合天生很匹配,以前客戶還能逃去外面做打通孔(指不定哪天還想換代工),后續(xù)封裝也很方便就能找別人做,現(xiàn)在你想獲得3D封裝中最好的互聯(lián)性能,那就乖乖的在臺(tái)積電TSV-less+CoW 混合鍵合做一套吧把米都給我交了!

2.嵌埋式封裝

嚴(yán)格來(lái)說(shuō)這不算是2.5D或者3D封裝,也不是什么未來(lái)技術(shù),嵌埋封裝顧名思義,就是把die嵌埋到封裝用的IC載板內(nèi)部,這樣的好處就是可以節(jié)省面積,方便小型化設(shè)計(jì),在芯片的載板內(nèi)部就集成了芯片所需外圍器件,節(jié)約了主板的空間。嵌埋式封裝的其實(shí)早在十幾年前就出現(xiàn)了,但是在過往的應(yīng)用中,嵌埋式技術(shù)主要是在載板中集成一些被動(dòng)元器件或者電源管理芯片,將芯片放到下層層壓基板之上,然后再制作鍍銅的通孔和聯(lián)線完成芯片的互聯(lián)并用特殊的環(huán)氧樹脂包覆芯片,之后再層壓上上方的基板完成整塊載板的制備,出售給客戶的時(shí)候就是一塊IC封裝載板。由于工藝中存在各種各樣的挑戰(zhàn)(IC載板本身就很難做,嵌埋式的載板是半加成法制作,要求高),這項(xiàng)技術(shù)被歸為比較小眾應(yīng)用,主要是一些電源管理芯片和藍(lán)牙芯片(或許該叫模塊,因?yàn)槌善沸酒陨砭褪且粋€(gè)包含了周邊器件的模塊)使用,幾乎沒有在數(shù)字芯片和大芯片領(lǐng)域見到。

除了工藝復(fù)雜的原因外,還有一個(gè)沒有被推廣開來(lái)的原因是嵌埋式封裝的主推者大部分都是載板廠商,畢竟這最符合他們的商業(yè)利益,但是載板廠自身對(duì)die的封裝積累不夠深,使得客戶也不敢把大芯片或者重要芯片交給他們做嵌埋,而封裝普遍認(rèn)為依靠RDL層代替載板做包覆/嵌埋芯片的載體更有前景也更符合利益(又回到我們開頭說(shuō)的第一點(diǎn)了)。而轉(zhuǎn)機(jī)就在隨著兼容PCB級(jí)別設(shè)備的面板級(jí)扇出工藝逐漸成熟,給載板廠帶來(lái)了可以用的RDL工藝,解決了部分封裝的難題,也帶來(lái)遠(yuǎn)超傳統(tǒng)嵌埋式互聯(lián)方法的互聯(lián)手段。

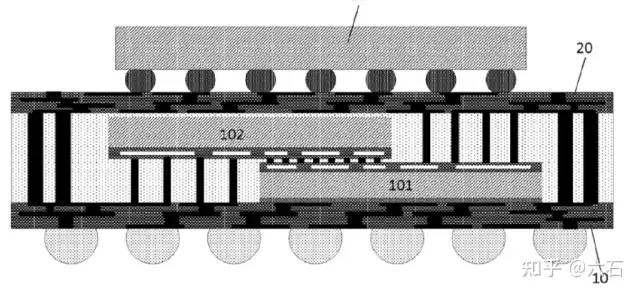

可能有人會(huì)說(shuō)這不是某為前段時(shí)間3D堆疊封裝的專利圖嗎?是的,不過我讀完專利之后,覺得更像是一個(gè)堆疊式的嵌埋封裝的專利,借由RDL技術(shù),嵌埋式封裝實(shí)現(xiàn)了一個(gè)創(chuàng)舉,就是不再需要TSV就能實(shí)現(xiàn)堆疊芯片之間以及和外界的互通(畢竟載板本身上下就能通訊),前文我們也提過,TSV其實(shí)是一個(gè)令人又愛又恨的東西,有114514人想干掉它,而借助嵌埋封裝,2.5D、3D封裝是有可能去掉TSV的。當(dāng)然,嵌埋封裝如何用于大芯片這個(gè)問題應(yīng)該還是沒有解決,我個(gè)人傾向于某為這個(gè)專利是給可穿戴、物聯(lián)網(wǎng)和電源管理類芯片準(zhǔn)備的,上圖頂上的芯片你把它想成是一個(gè)手表芯片,它的載板里借助嵌埋封裝封裝了原本在主板上的SRAM和電源管理芯片,現(xiàn)在一個(gè)芯片就成為一個(gè)可用的模塊,剩下的空間給電池,不是美滋滋嗎?

事實(shí)上,果子今年已經(jīng)準(zhǔn)備類似的封裝了,聯(lián)系了某載板廠,最快下半年就可能可以見到落地了,應(yīng)該是應(yīng)用在耳機(jī)上,把原本就很小的系統(tǒng)再縮小一點(diǎn)。另外,某為也一直在和某大陸載板廠合作搞嵌埋式封裝,做的是一種類似Ti MicroSiP的產(chǎn)品,MicroSiP是嵌埋式領(lǐng)域最成功的一顆芯片(模塊)了,借助嵌埋技術(shù),TI將其電源管理IC嵌入到基板中,并將無(wú)源元器件安裝在封裝體的頂部,整個(gè)模塊體積小的驚人,某某的基站我印象里好像用了不少。

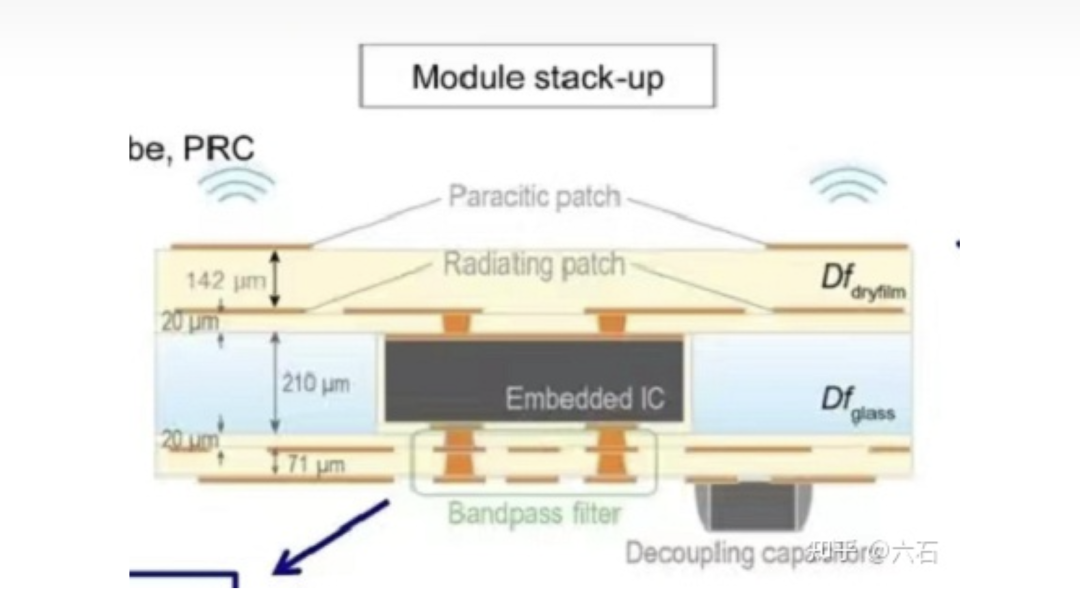

當(dāng)然還有一種可能,這個(gè)技術(shù)是為射頻領(lǐng)域準(zhǔn)備的,射頻領(lǐng)域?qū)iP、嵌埋式的探索一直沒有停止,把天線、IC、各種濾波器、PA集成在一個(gè)模組甚至一個(gè)”芯片“(的載板)里一直是業(yè)界很想做到的,上圖就是老美對(duì)5G射頻IC的一個(gè)研究,它的形式就是把IC嵌埋在玻璃和層壓載板中,同時(shí)載板上集成了很多器件。某為做做這類芯片,非常合理

3.14+14>7?

這部分我純粹在”瞎扯“了,以下內(nèi)容如讓您感到亂說(shuō),以您為準(zhǔn),在說(shuō)這部分前,有篇文章推薦大家看看,馬愷聲老師的《我親歷的Chiplet拆解難題》,他的這篇很好的探討了chiplet、先進(jìn)封裝在實(shí)際應(yīng)用中的遇到的種種情況和考量。

來(lái)源:知乎

https://zhuanlan.zhihu.com/p/514519818

原文始發(fā)于微信公眾號(hào)(艾邦半導(dǎo)體網(wǎng)):先進(jìn)封裝雜談——2.5D/3D先進(jìn)封裝