- 成功使用電介質納米立方體單層膜實現多層電容器結構的薄型化

- 開發了一種使用石墨烯作為內部電極代替傳統金屬電極的層狀結構

- 為多層陶瓷電容器的小型化做出貢獻

近年來,隨著智能手機、平板電腦等小型電子設備的性能迅速提高,這些設備內置的電子元件需要進一步小型化。 MLCC 是最重要的電子元件之一,目前每部智能手機大約使用 1,000 個 MLCC。 MLCC的內部具有介電層和電極層交替層疊的結構,為了縮小尺寸、提高性能,使各層變薄并增加層數是一個重要的開發挑戰。

為了實現MLCC的小型化并提高其性能,工業界和學術界正在研究使用介電層和電極層材料的各種組合來減薄和堆疊MLCC。 目前使用BTO作為介電層的MLCC,其層狀結構是通過將作為介質層的原料的BTO粉末和作為電極層的原料的金屬粉末交替層疊并在1000度以上的高溫下烘烤的工藝形成的。然而,電介質層和電極層的厚度已經不足1μm,接近原料粉末顆粒的尺寸(數百nm),并且電介質層的絕緣性能因變薄而劣化等問題。以目前的原料粉末和層壓工藝,已接近進一步薄型化的極限。 因此,面臨的挑戰是開發一種新的分層工藝技術,將介電層和電極層的厚度降低至納米級厚度,同時繼續細化用作原材料的BTO粉末并保持MLCC的可靠性。

日本產業技術綜合研究所(AIST)先進功能材料研究所研究員Hiroki Itasaka、高級研究員劉軒、高級研究員Kenichi Mimura、Koichi Hamamoto開發了介電材料鈦酸鋇(BTO)立方單晶(納米立方)單層薄膜與多層石墨烯薄膜的交替層壓工藝技術。

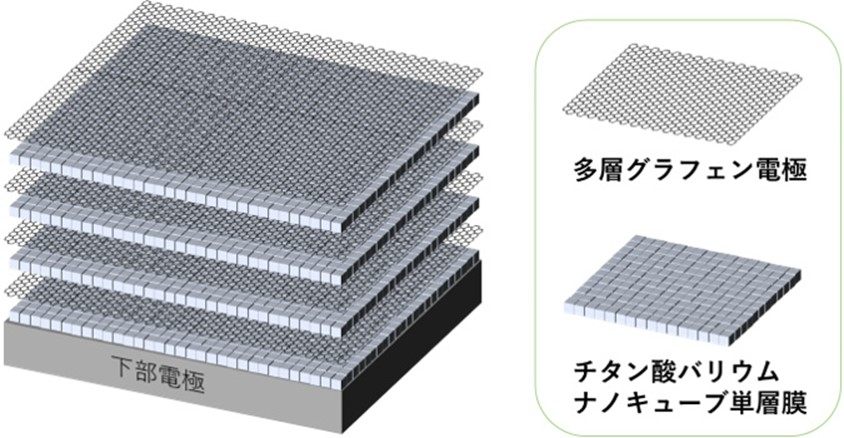

開發的疊層結構示意圖

在本研究開發的技術中,超薄層狀結構是由尺寸約為20納米的BTO納米立方體二維排列的單層膜和厚度為2至3納米的多層石墨烯膜交替排列而成。該技術有望成為實現多層陶瓷電容器(MLCC)內部介電層和電極層交替層壓結構的大幅薄化的基礎技術。

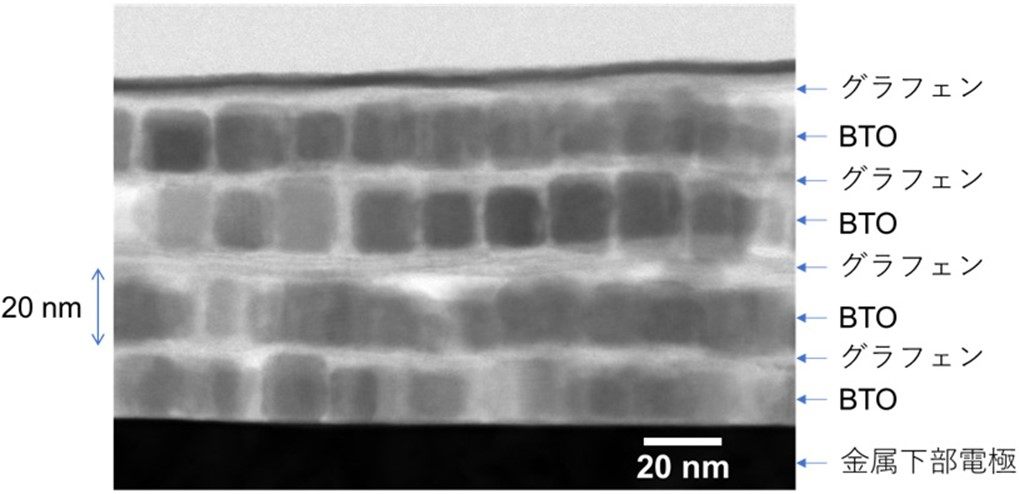

在這項技術中,AIST專注于二維碳材料石墨烯的優異導電性,并發明了一種通過將其與單層BTO納米立方體相結合,創建極薄電極層和介電層的交替層壓結構的方法。通過交替重復將利用上述成膜技術生產的BTO納米立方體單層膜轉移到下電極基板上和將片狀多層石墨烯轉移到其上的過程,在其內部形成類似于堆疊結構的石墨烯層。可以制造BTO納米立方體單層膜交替層壓的MLCC/結構。 圖1顯示了使用掃描透射電子顯微鏡觀察到的所制造的層狀結構的橫截面照片。

圖1 本研究制備的石墨烯/BTO納米立方單層交替疊層結構的截面觀察照片

從圖1可以看出,形成了厚度約為20 nm的均勻BTO納米立方介電層,并在其頂部沉積了厚度為2-3 nm的多層石墨烯層。 通過重復這個過程,成功地創建了一種單層 BTO 納米立方體和多層石墨烯交替堆疊的結構。 在本次制作的交替層疊結構中,與使用BTO作為介電層的MLCC內部的傳統層疊結構相比,介電層和電極層的厚度分別減少到1/10和1/100以下(介質層和電極層的最小厚度均為數百納米))。 減小介電層和電極層的厚度對于減小MLCC的尺寸和提高性能至關重要,但這會導致電容器的可靠性下降的問題。 到目前為止,我們沒有使用傳統的金屬電極,而是使用厚度約為2至3納米的多層石墨烯作為電極層,而且已發現它可以減少由于電極材料滲透到 BTO 顆粒之間的間隙而引起的漏電流。 加上這種漏電流減少效果,此次開發的技術有望成為MLCC內部多層結構薄型化技術的突破。

?

日本產業技術綜合研究所(AIST)一直致力于開發作為MLCC介電層主要原料的微小BTO粉末的合成技術,以及由合成粉末形成薄膜的成膜技術。 到目前為止,已經成功利用水熱法合成了納米尺寸的BTO立方單晶(納米立方體)(參考文獻1),我們也成功地利用水熱法合成了納米尺寸的BTO立方單晶(納米立方體)(參考文獻1).我們開發了一種成膜技術,可制造厚度約為20 nm的單層薄膜,其中BTO納米立方體以二維方式規則排列(參考文獻2)。 BTO納米立方體比一般的BTO納米顆粒具有更高的結晶度,即使在低于1000℃的相對較低的加工溫度下,也有望表現出優異的介電性能。 此外,為了使用傳統的BTO粉末形成致密的薄膜,需要在高溫下進行熱處理,但是通過規則地排列均勻尺寸和形狀的BTO納米立方體,可以進行熱處理。還可以無需熱處理即可獲得致密的薄膜。 這次,為了將通過這些技術獲得的BTO納米立方單層膜用作MLCC內部的介電層,AIST開發了一種將其與電極層交替堆疊的技術。

這項研究和開發得到了日本學術振興會(JSPS)科學研究補助金 JP20H02446(2020-2022)和新能源和產業技術綜合開發組織(NEDO)合同項目 JPNP20005(2021-2023)的支持。

AIST表示將繼續優化熱處理等工藝,提高疊層結構電容器的性能,通過開發可大規模生產的工藝,實現下一代工藝技術,從而實現 MLCC 的大幅小型化和容量增加。

論文信息

出版物:Applied Physics Letters

論文標題:Ultra-thin barium titanate nanocrystal monolayer capacitor with graphene electrode

作者:Hiroki Itasaka*, Zheng Liu, Ken-ichi Mimura, and Koichi Hamamoto

*Corresponding author

DOI:10.1063/5.0156549

參考

1. F. Dang, K. Mimura, K. Kato, H. Imai, S. Wada, H. Haneda, and M. Kuwabara,?Nanoscale,?4?1344 (2012).

2. H. Itasaka, K. Mimura, and K. Kato,?Nanomaterials,?8, 739, (2018).