本文將詳述半導(dǎo)體后端(Back-End)工藝系列中封裝技術(shù)的不同等級、作用和演變過程。

1有源元件:一種需要外部電源才能實現(xiàn)其特定功能的器件,就像半導(dǎo)體存儲器或邏輯半導(dǎo)體。

2無源元件:一種不具備放大或轉(zhuǎn)換電能等主動功能的器件。

3電容器(Capacitor):一種儲存電荷并提供電容量的元件。

4錫(Solder):一種低熔點金屬,支持電氣和機械鍵合。

5引線(Lead):從電路或元件終端向外引出的導(dǎo)線,用于連接至電路板。

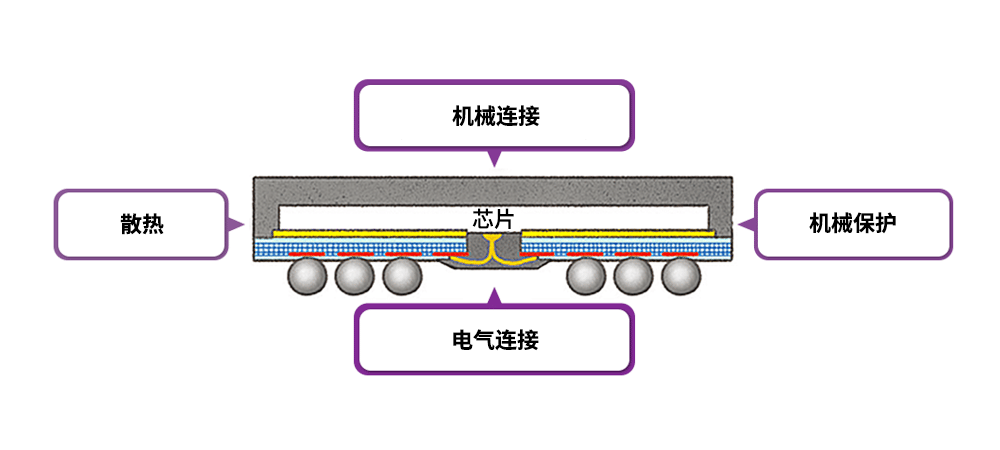

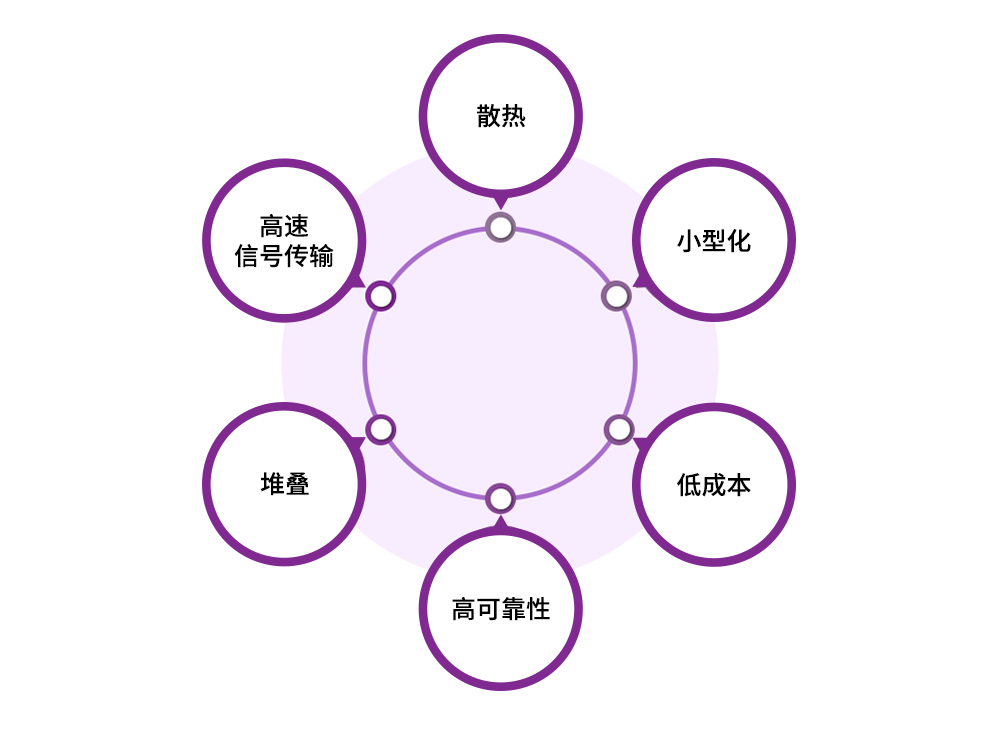

同時,封裝需將半導(dǎo)體芯片和器件產(chǎn)生的熱量迅速散發(fā)出去。在半導(dǎo)體產(chǎn)品工作過程中,電流通過電阻時會產(chǎn)生熱量。如圖3所示,半導(dǎo)體封裝將芯片完全地包裹了起來。如果半導(dǎo)體封裝無法有效散熱,則芯片可能會過熱,導(dǎo)致內(nèi)部晶體管升溫過快而無法工作。因此,對于半導(dǎo)體封裝技術(shù)而言,有效散熱至關(guān)重要。隨著半導(dǎo)體產(chǎn)品的速度日益加快,功能日益增多,封裝的冷卻功能也變得越來越重要。

首先,由于散熱已經(jīng)成為封裝工藝的一個重要因素,因此人們開發(fā)出了熱傳導(dǎo)6性能較好的材料和可有效散熱的封裝結(jié)構(gòu)。

6熱傳導(dǎo):指在不涉及物質(zhì)轉(zhuǎn)移的情況下,熱量從溫度較高的部位傳遞到相鄰溫度較低部位的過程。

可支持高速電信號傳輸的封裝技術(shù)也成為了一種重要發(fā)展趨勢,因為封裝會限制半導(dǎo)體產(chǎn)品的速度。例如,將一個速度達每秒20千兆 (Gbps) 的半導(dǎo)體芯片或器件連接至僅支持每秒2千兆(Gbps) 的半導(dǎo)體封裝裝置時,系統(tǒng)感知到的半導(dǎo)體速度將為每秒2千兆 (Gbps)。由于連接至系統(tǒng)的電氣通路是在封裝中創(chuàng)建,因此無論芯片的速度有多快,半導(dǎo)體產(chǎn)品的速度都會極大地受到封裝的影響。這意味著,在提高芯片速度的同時,還需要提升半導(dǎo)體封裝技術(shù),從而提高傳輸速度。這尤其適用于人工智能技術(shù)和5G無線通信技術(shù)。鑒于此,倒片封裝7和硅通孔(TSV)8等封裝技術(shù)應(yīng)運而生,為高速電信號傳輸提供支持。

7倒片封裝(Flip Chip):一種通過將凸點朝下安裝于基板上,將芯片與基板連接的互連技術(shù)。

8硅通孔(TSV):一種可完全穿過硅裸片或晶圓實現(xiàn)硅片堆疊的垂直互連通道。

9系統(tǒng)級封裝(SiP):一種將多個器件整合在單個封裝體內(nèi)構(gòu)成一個系統(tǒng)的封裝技術(shù)。

封裝技術(shù)還呈現(xiàn)半導(dǎo)體器件小型化的發(fā)展趨勢,即縮小產(chǎn)品尺寸。隨著半導(dǎo)體產(chǎn)品逐漸被用于移動甚至可穿戴產(chǎn)品,小型化成為客戶的一項重要需求。為了滿足這一需求,許多旨在減小封裝尺寸的技術(shù)隨之而誕生。

此外,半導(dǎo)體產(chǎn)品正越來越多地應(yīng)用于各種環(huán)境中。除了健身房、辦公室或住宅等日常環(huán)境,熱帶雨林、極地地區(qū)、深海甚至太空等環(huán)境中也能見到半導(dǎo)體的身影。由于封裝的基本作用是保護半導(dǎo)體芯片和器件,因此需要開發(fā)高度可靠的封裝技術(shù),確保半導(dǎo)體產(chǎn)品在此類極端環(huán)境下也能正常工作。

最后,由于半導(dǎo)體封裝是最終產(chǎn)品,封裝技術(shù)不僅要實現(xiàn)預(yù)期功能,還要具有較低的制造成本。

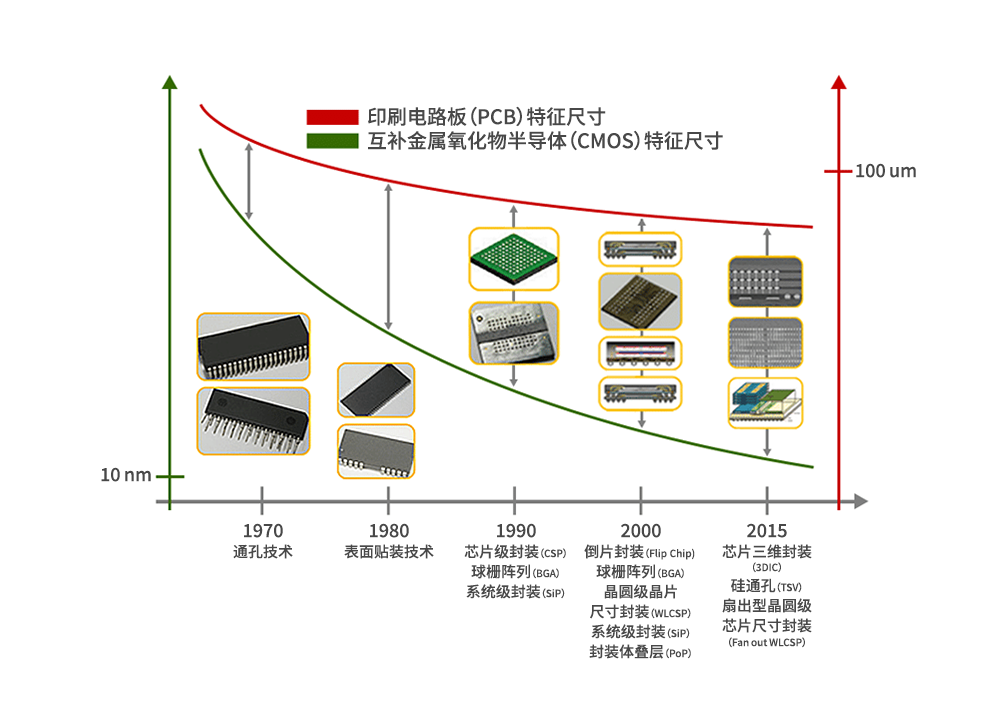

除了上述旨在推進封裝技術(shù)特定作用的發(fā)展趨勢,促使封裝技術(shù)發(fā)生演變的另一個驅(qū)動力是整個半導(dǎo)體行業(yè)的發(fā)展。在圖5中,紅色線條表示自20世紀70年代以來裝配過程中安裝的印刷電路板(PCB)10的特征尺寸變化情況,綠色線條則表示晶圓上CMOS晶體管的特征尺寸變化情況。縮小特征尺寸有助在印刷電路板和晶圓上繪制更小的圖案。

10印刷電路板(PCB):由電路組成的半導(dǎo)體板,且元件焊接在電路板表面。這些電路板通常用于電子設(shè)備中。

由于主板以面板的形式制造,且受到成本節(jié)約策略等因素的影響,印刷電路板的特征尺寸變化不大。然而,隨著光刻技術(shù)的進步,CMOS晶體管的特征尺寸大幅縮小,這使得CMOS晶體管的尺寸與印刷電路板的尺寸差距逐漸拉大。但問題在于,半導(dǎo)體封裝技術(shù)需要對從晶圓上切割下來的芯片進行個性化定制,并將其安裝到印刷電路板上,因此就需要彌補印刷電路板和晶圓之間的尺寸差距。過去,兩者在特征尺寸上的差異并不明顯,因而可以使用雙列直插式封裝(DIP)11或鋸齒型單列式封裝(ZIP)12等通孔技術(shù),將半導(dǎo)體封裝引線插入印刷電路板插座內(nèi)。然而,隨著兩者特征尺寸差異不斷擴大,就需要使用薄型小尺寸封裝(TSOP)等表面貼裝技術(shù)(SMT)13將引線固定在主板表面。隨后,球柵陣列(BGA)、倒片封裝、扇出型晶圓級芯片尺寸封裝(WLCSP)14及硅通孔(TSV)等封裝技術(shù)相繼問世,以彌補晶圓和主板之間不斷擴大的尺寸差異。

11雙列直插式封裝(DIP):一種電氣連接引腳排列成兩行的封裝技術(shù)。

12鋸齒型單列式封裝(ZIP):一種引腳排列成鋸齒型的封裝技術(shù),是雙列直插式封裝的替代技術(shù),可用于增加安裝密度。

13表面貼裝技術(shù)(SMT):一種通過焊接將芯片安裝到系統(tǒng)板表面的封裝方法。

14晶圓級晶片尺寸封裝(WLCSP):一種在晶圓級封裝集成電路的技術(shù),是倒片封裝技術(shù)的一個變體。扇出型晶圓級芯片尺寸封裝(WLCSP)的特點在于連接超出(“扇出”)芯片表面。

一般來說,新芯片的開發(fā)和新封裝技術(shù)的應(yīng)用不會同時進行。原因在于,如果芯片和封裝均未經(jīng)過測試,那么一旦在封裝完成后出現(xiàn)問題,就很難確定問題的原因。鑒于此,業(yè)界會使用已知缺陷較少的現(xiàn)有量產(chǎn)芯片來測試新的封裝技術(shù),以單獨驗證封裝技術(shù)。在封裝技術(shù)得到驗證后,才會將其應(yīng)用于新芯片的開發(fā),進而再生產(chǎn)半導(dǎo)體產(chǎn)品。

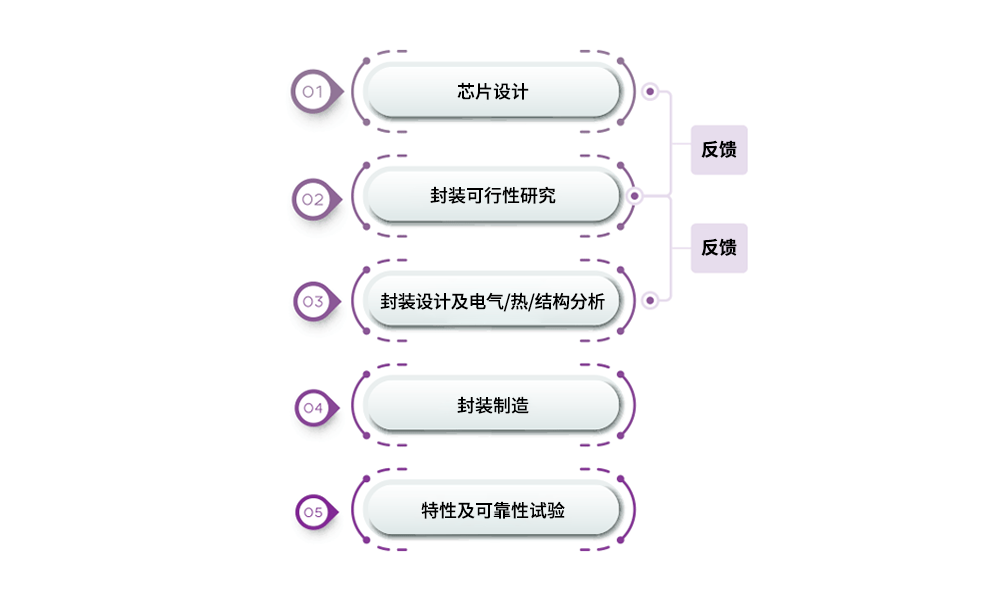

圖6展示了針對新芯片的封裝技術(shù)開發(fā)流程。通常,在制造半導(dǎo)體產(chǎn)品時,芯片設(shè)計和封裝設(shè)計開發(fā)會同時進行,以便對它們的特性進行整體優(yōu)化。鑒于此,封裝部門會在芯片設(shè)計之前首先考慮芯片是否可封裝。在可行性研究期間,首先對封裝設(shè)計進行粗略測試,以對電氣評估、熱評估和結(jié)構(gòu)評估進行分析,從而避免在實際量產(chǎn)階段出現(xiàn)問題。在這種情況下,半導(dǎo)體封裝設(shè)計是指基板或引線框架的布線設(shè)計,因為這是將芯片安裝到主板的媒介。

封裝部門會根據(jù)封裝的臨時設(shè)計和分析結(jié)果,向芯片設(shè)計人員提供有關(guān)封裝可行性的反饋。只有完成了封裝可行性研究,芯片設(shè)計才算完成。接下來是晶圓制造。在晶圓制造過程中,封裝部門會同步設(shè)計封裝生產(chǎn)所需的基板或引線框架,并由后段制造公司繼續(xù)完成生產(chǎn)。與此同時,封裝工藝會提前準備到位,在完成晶圓測試并將其交付到封裝部門時,立即開始封裝生產(chǎn)。

原文始發(fā)于微信公眾號(艾邦半導(dǎo)體網(wǎng)):半導(dǎo)體后端工藝|半導(dǎo)體封裝的作用、工藝和演變