Chiplet是將一類滿足特定功能的die,通過die-to-die內部互聯技術實現多個模塊芯片與底層基礎芯片封裝在一起,進而形成一個系統芯片。它能在不改變制程的前提下提升芯片集成度,提高算力并保證芯片生產良率,相比傳統SoC在設計靈活度、設計與生產成本、上市周期等方面優勢明顯,有望成為后摩爾時代我國集成電路彎道超車的重要途徑。

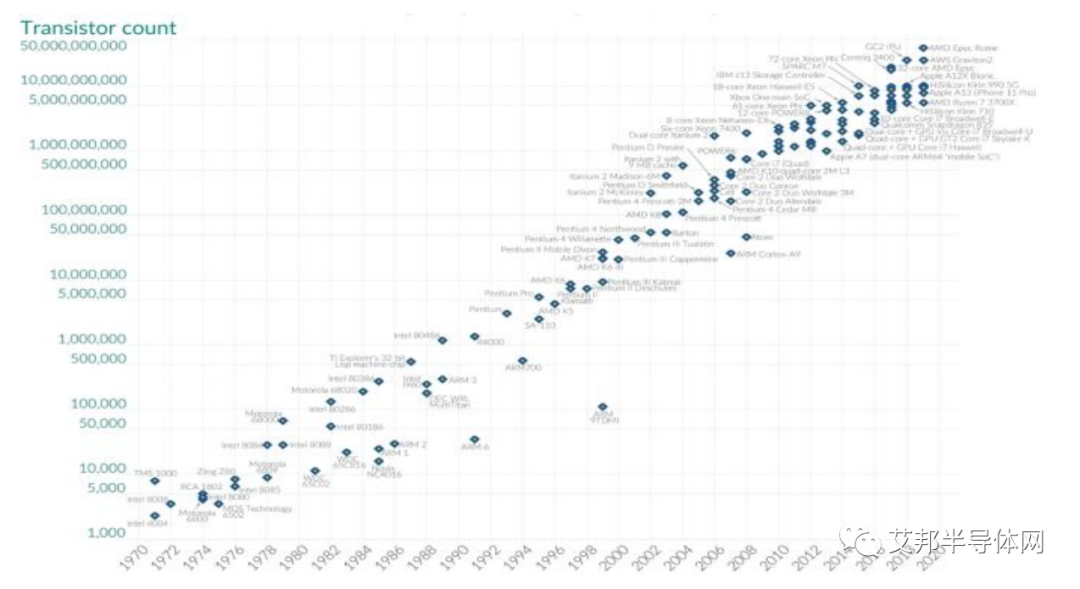

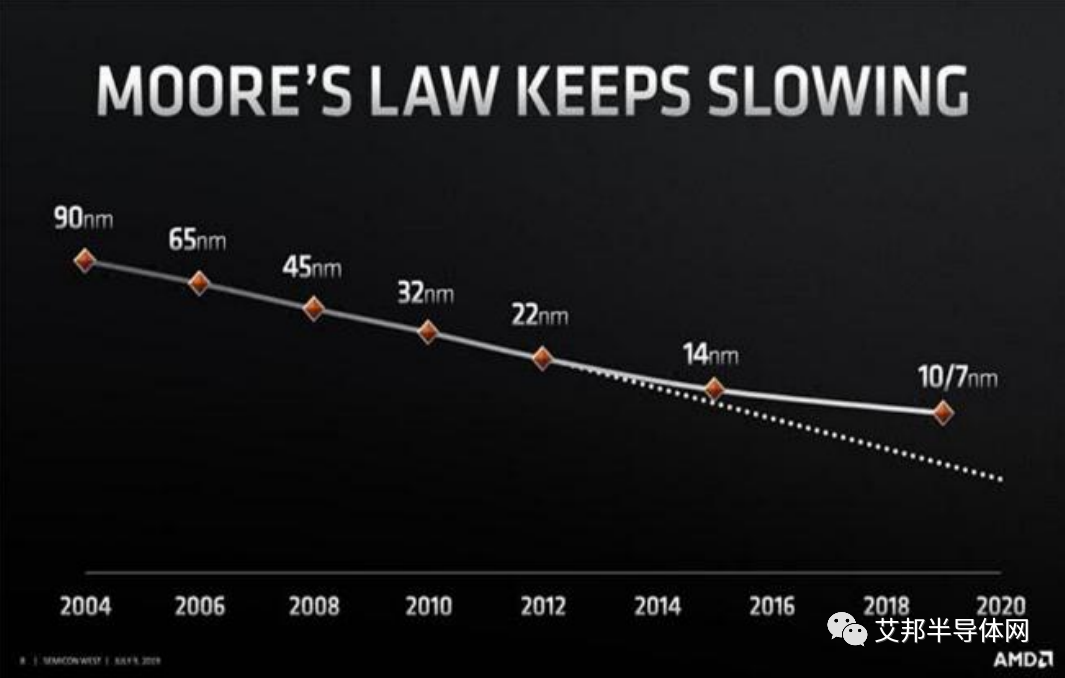

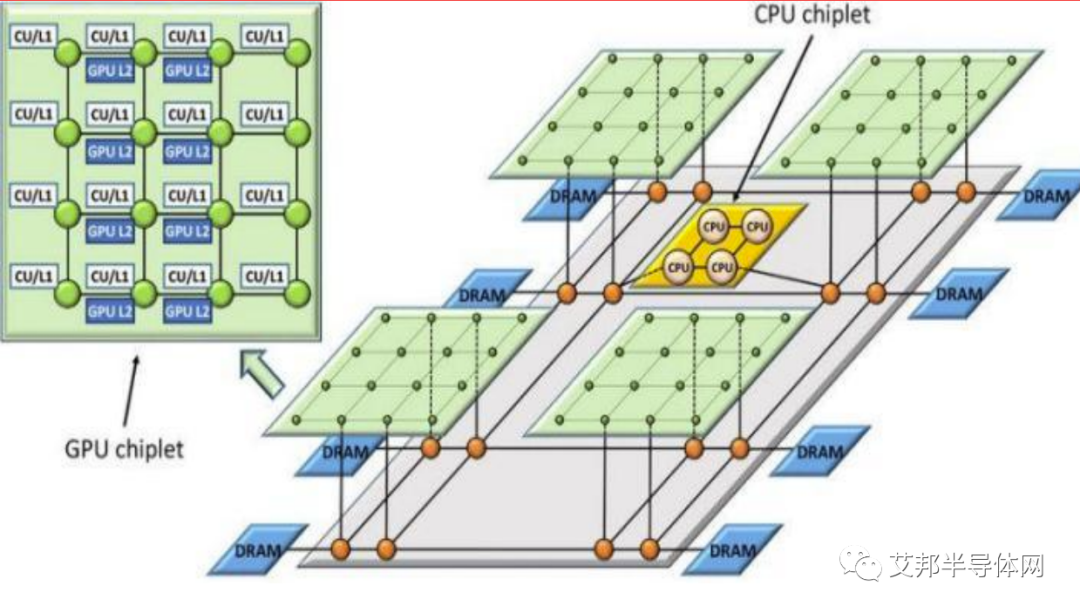

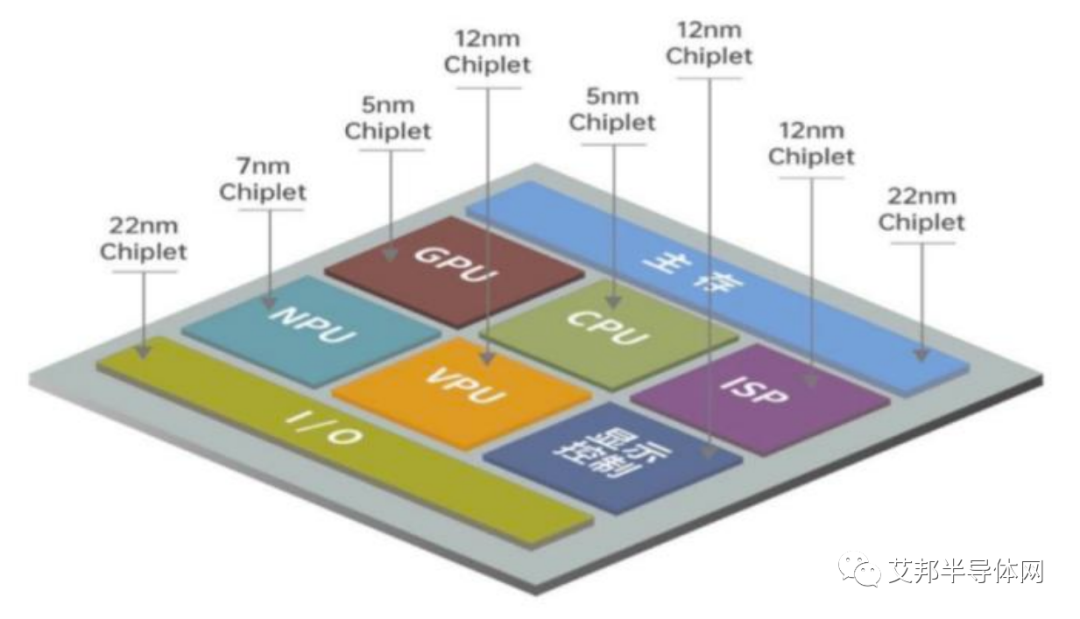

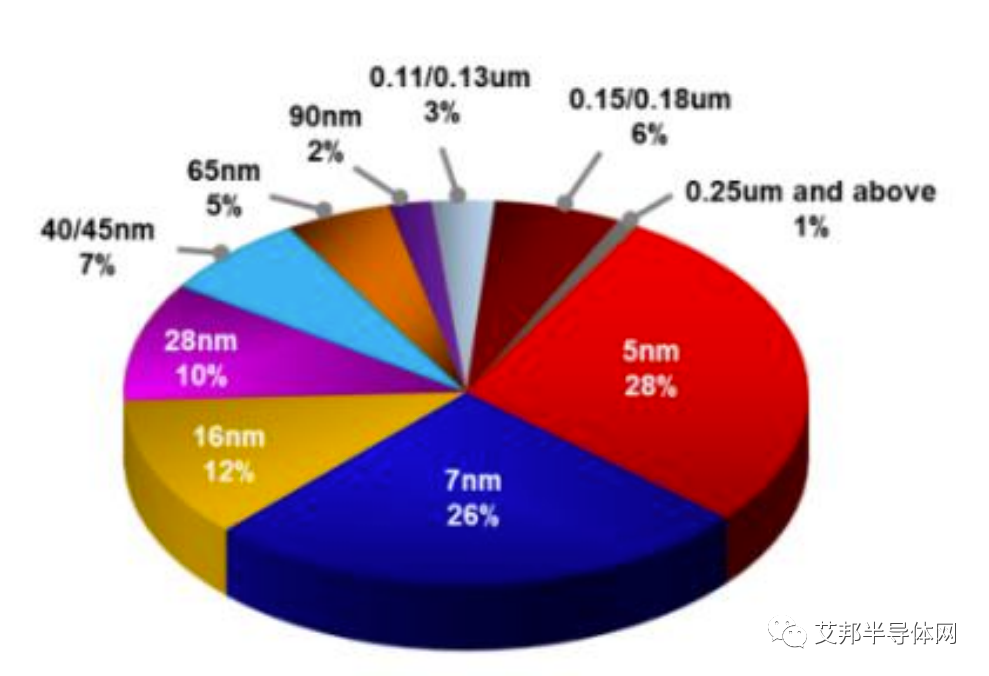

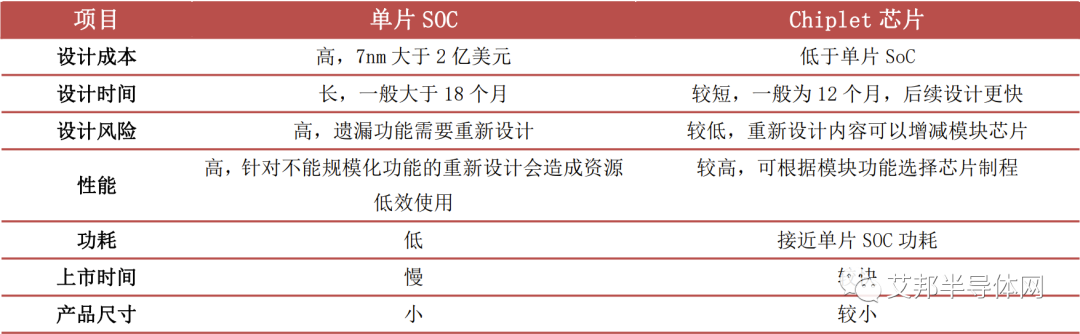

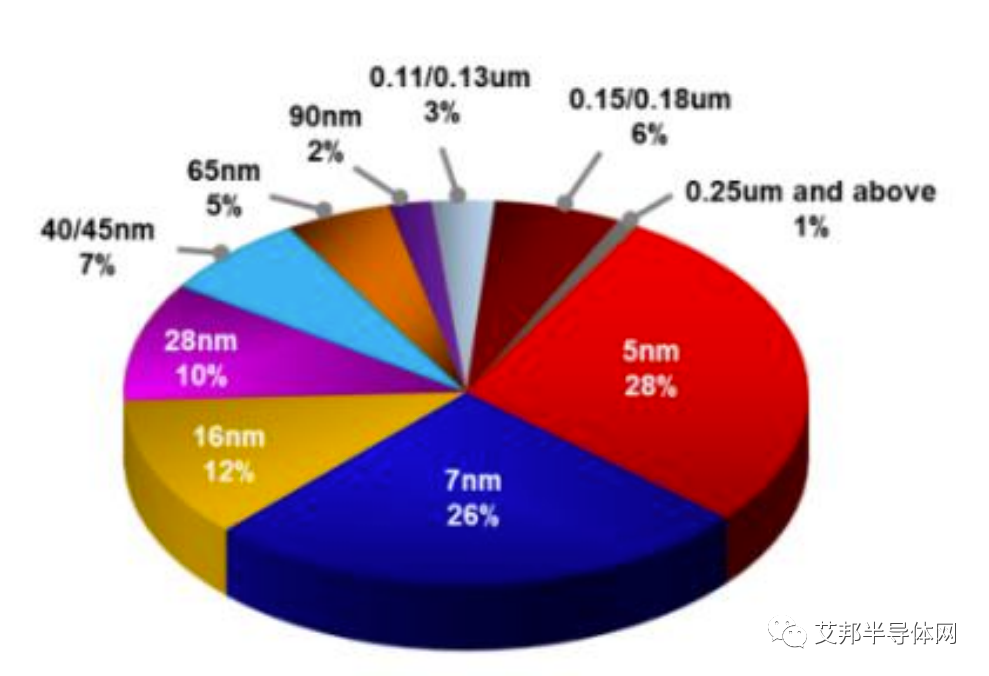

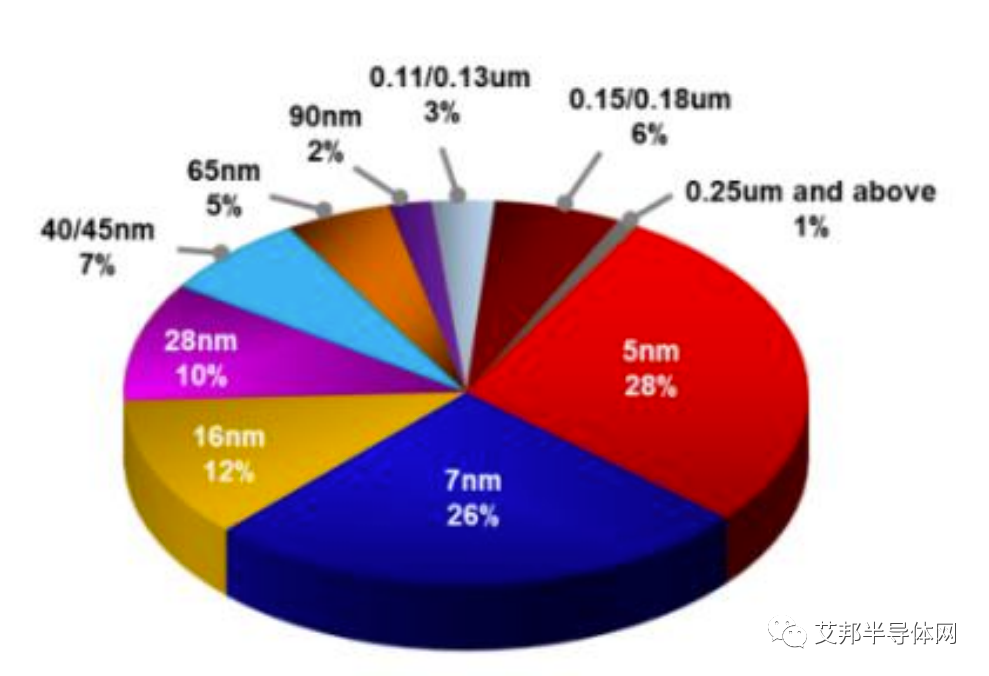

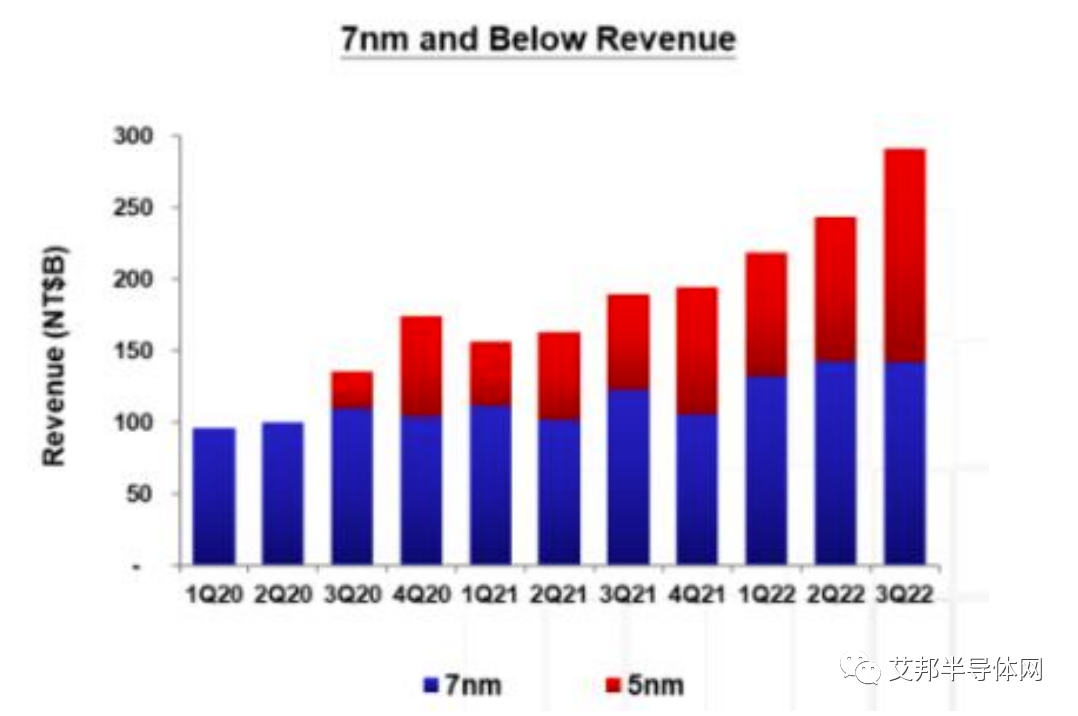

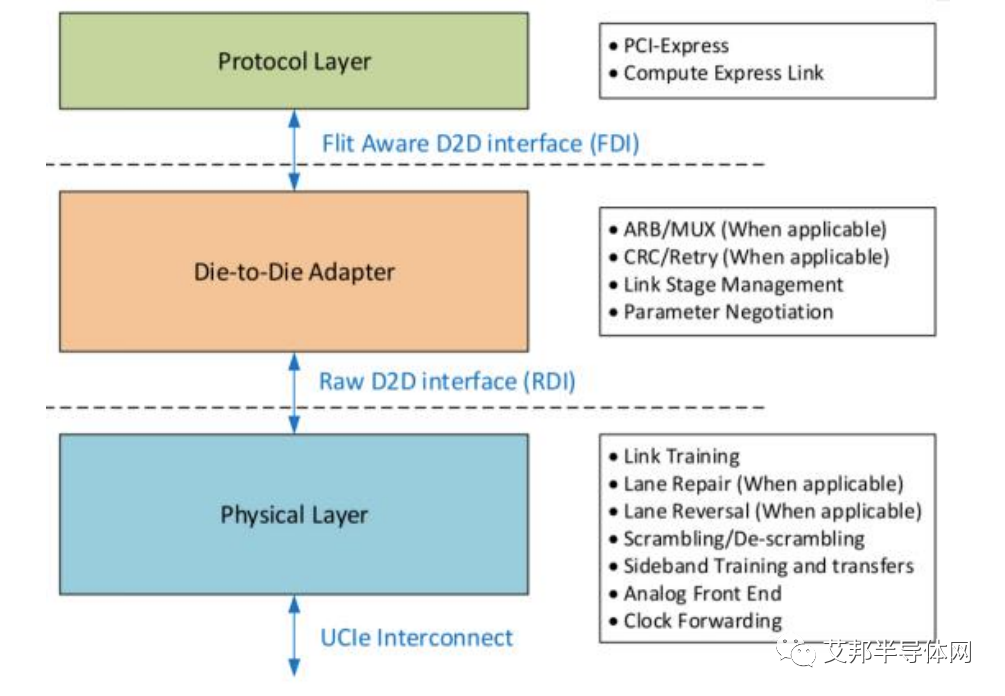

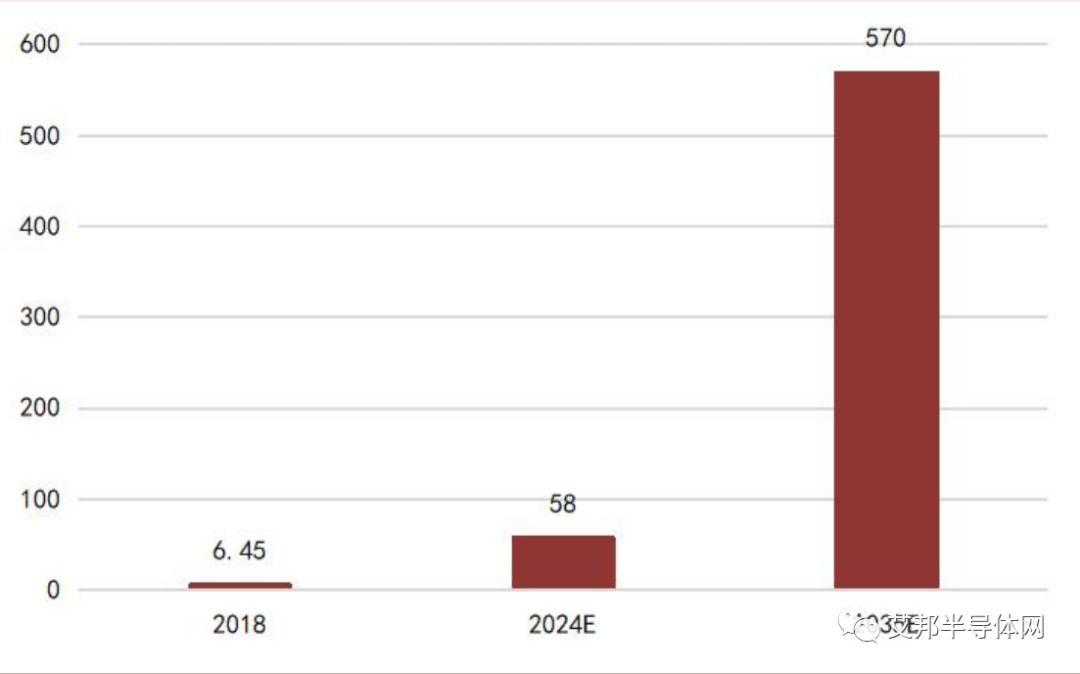

1. Chiplet為后摩爾時代提升芯片算力與集成度的重要途徑 摩爾定律指引過去幾十年集成電路產業發展。摩爾定律由英特爾創始人之一的戈登·摩爾(Gordon Moore)提出,其核心內容為:在價格不變時,集成電路上可以容納的晶體管數量每18-24個月便會增加一倍,即:處理器性能大約每兩年翻一倍,同時價格下降為之前的一半。在過去幾十年,摩爾定律指引著集成電路產業發展。隨著工藝進步,集成電路上晶體管密度不斷提升,驅動計算機性能保持幾何級數增長,而性能的快速提升則推動芯片價格迅速下降。 “摩爾定律”發展陷入瓶頸,集成電路進入后摩爾時代。從1987年的1um制程至2015年的14nm制程,集成電路制程迭代大致符合“摩爾定律”的規律。但自2015年以來,集成電路先進制程的發展開始放緩,7nm、5nm、3nm制程的量產進度均落后于預期。隨著臺積電宣布2nm制程工藝實現突破,集成電路制程工藝已接近物理尺寸的極限,摩爾定律發展陷入瓶頸,行業進入了“后摩爾時代”。 圖1:摩爾定律在過去幾十年指引集成電路產業發展(資料來源:維基百科,東莞證券研究所) 圖2:摩爾定律逐步放緩(資料來源:AMD,東莞證券研究所) Chiplet可在不改變制程的前提下提升算力,且保證芯片良率。Chiplet俗稱“芯粒”,又稱“小芯片組”,從字面意義上可以理解為“粒度更小的芯片”。它是將一類滿足特定功能的die,通過die-to-die內部互聯技術實現多個模塊芯片與底層基礎芯片封裝在一起,進而形成一個系統芯片。它可以有效提升芯片的集成度,是在不改變制程的前提下提升算力,并且保證芯片生產良率的一種手段。 圖3:GPU、CPU Chiplet示意圖(資料來源:電子工程世界,東莞證券研究所) 圖4:集成多制程工藝器件的Chiplet異構處理器(資料來源:芯原股份年報,東莞證券研究所) 與傳統SoC相比,Chiplet在設計靈活度、設計與生產成本、上市周期等方面優勢明顯。傳統SoC,即系統級單芯片,是將多個負責不同類型計算任務的計算單元,通過光刻的形式制作到同一塊晶圓上。隨著摩爾定律放緩,傳統的SoC的生產周期越來越長,在成本大幅增加的情況下性能提升幅度有限,行業接近制造瓶頸;與SoC不同,Chiplet是將一塊原本復雜的SoC芯片,從設計時就先按照不同的計算單元或功能單元對其進行分解,然后每個單元選擇最適合的半導體制程工藝進行分別制造,再通過先進封裝技術將各個單元彼此互聯,最終集成封裝為一個系統級芯片組。 相比傳統的SoC,Chiplet能夠有效降低研發、設計與制造成本,并顯著提升芯片良率。英特爾公司高級副總裁、中國區董事長王銳在2022世界集成電路大會上表示,Chiplet技術是產業鏈生產效率進一步優化的必然選擇。“不但提高芯片制造良品率,利用最合適的工藝滿足數字、模擬、射頻、I/O等不同技術需求,而且更將大規模的SoC按照不同的功能,分解為模塊化的芯粒,減少重復的設計和驗證環節,大幅度降低設計復雜程度,提高產品迭代速度。且有利于后續的產品迭代,縮短上市周期。” Chiplet優勢一:降低芯片設計的復雜程度,有效降低研發與設計成本。Chiplet芯粒設計靈活,且可重復使用,通過將已知的合格芯片裸片進行集成,能夠縮短芯片的研發與設計周期,降低研發設計成本。據悉,設計28nm芯片的平均成本為4,000萬美元,設計7nm芯片的成本上升至2.17億美元。而The Linley Group的白皮書《Chiplets Gain Rapid Adoption: Why Big Chips Are Getting Small》中提出,Chiplet技術可以將大型7nm設計的成本降低25%。; Chiplet優勢二:提升良率。SoC將多個不同類型計算任務的計算單元以光刻形式集成在同一片晶圓上,隨著先進制程不斷推進,單位面積上集成的晶體管數量越來越多,設計周期越來越廠,芯片面積也在加大。高性能計算等領域巨大運算需求推動邏輯芯片運算核心數量上升,配套SRAM容量、I/O數量隨之提升。隨著芯片面積的加大和集成的晶體管數量增多,對制造過程中的芯片良率提出較高挑戰,讓芯片生產中的工藝誤差和加工缺陷顯得愈發明顯,一個微小的缺陷就可能導致整個大芯片報廢。Chiplet技術將大芯片分割成不同功能模塊進行獨立制造,通過將廣泛的、成熟的芯片裸片進行集成,只需保障各個被集成的成熟芯片良率即可,能夠降低先進制程的研發與制造風險,有效提升良率。 Chiplet優勢三:大幅降低芯片制造成本。SoC中的邏輯計算單元對性能要求高,整體依賴先進制程,具有極高的生產壁壘與制造成本;Chiplet方案則可針對不同的模塊采取不同的合適的制程,分開制造,最后采用先進封裝技術進行組裝,能大幅降低芯片的制造成本。 圖5:Chiplet晶圓設計方案(資料來源:EE Times,東莞證券研究所) 圖6:Chiplet方案能顯著提升芯片良率(資料來源:WikiChip,東莞證券研究所) 后摩爾時代,Chiplet成為提高芯片算力與集成度的重要途徑。后摩爾時代,隨著集成度提升,SoC開始在供電、功耗和散熱等方面面臨挑戰,芯片全流程設計成本大幅增加,而制程工藝接近極限,每次迭代升級都需要付出極大的額外成本,而隨著性能提升,發熱功耗等方面的問題也日益凸顯,繼續追求極致工藝的意義已經不大。Chiplet作為當下較受關注的半導體發展方向,可有效降低能夠有效降低芯片設計與制造的門檻,提升良率和節約成本,因此成為摩爾定律趨緩背景下提升芯片集成度與算力的重要途徑。 表1:Chiplet芯片與SoC比較(資料來源:《后摩爾時代Chiplet技術的演進與挑戰》,東莞證券研究所) 2. 海外科技領域制裁加劇,Chiplet助力國內半導體產業彎道超車 海外科技領域制裁加劇,國內半導體先進制程發展受限。近年來中美摩擦加劇,美國針對中國在高科技領域的限制增多,企圖通過加大制裁力度來限制國內集成電路產業發展。2020年12月,美國將中芯國際列入“實體清單”,限制企業14nm及以下半導體制程的擴產;2022年8月,美國簽署《芯片與科學法案》,主要用于增強美國本土晶圓廠的競爭力,并明確規定獲得美國政府補貼的企業,10年內不得在中國大陸擴產28nm以下的芯片制造。《芯片法案》的簽署,進一步加劇了中美在高科技領域的脫鉤程度,導致國內芯片先進制程發展受到限制。 表2:海外制裁限制我國半導體產業發展(資料來源:《中美戰略競爭下兩岸半導體產業發展問題研究》,美國商務部,東莞證券研究所) 先進制程是提高算力的必要途徑,臺積電先進制程占比不斷提高。近年來,人工智能、大數據、自動駕駛和AIoT等下游應用的不斷發展,對芯片處理與運算能力提出更高的要求,高性能、低功耗成為先進制程的發展方向。從全球晶圓代工龍頭臺積電的各制程營收占比來看,近年來臺積電先進制程營收占比不斷提升:2022年前三季度,臺積電實現營收6,131.4億元新臺幣,其中5nm制程占比28%,7nm制程占比26%。而分地區看,近年來臺積電來自大陸市場的營收占比有所下滑。2022年,美國市場成為臺積電最大來源,營收規模達1.49萬億新臺幣,占比65.96%,中國大陸市場營收2,451.68 億元,占比10.82%,相比2020年的17.45%大幅下滑。 圖7:臺積電22Q3收入分布(按制程節點劃分)(資料來源:臺積電法說會,東莞證券研究所) 圖8:臺積電7nm及以下制程占比不斷提升(資料來源:臺積電法說會材料,東莞證券研究所) 海外制裁加劇,Chiplet有望助力國內半導體產業實現彎道超車。通過先進制程可實現芯片性能的迅速提升,因此全球晶圓代工龍頭先進制程占比不斷提升,而中國大陸先進制程發展受到限制。Chiplet技術僅對核心Chip采用先進制程,其他如存儲芯片、I/O芯片采用成熟制程,有效降低對先進制程的依賴,有望成為我國半導體產業彎道超車的突破口。2022年12月,我國第一個原生Chiplet技術標準——《小芯片接口總線技術要求》團體標準正式發布,這個標準涵蓋了多種應用場景的小芯片接口總線技術要求,包括總體概述、接口要求、鏈路層、適配層、物理層和封裝要求等,能夠靈活應對不同的應用場景、適配不同能力的技術供應商。《總線技術要求》的發布,對于我國集成電路產業延續“摩爾定律”,打破先進制程限制因素,提升產業綜合競爭力,具有重要意義。 3. 新互聯標準提供行業規范,Chiplet市場規模有望快速擴張 新互聯標準UCle出臺,為集成不同芯片提供標準與技術支持。盡管Chiplet優勢明顯,但由于過去Chiplet互聯標準并不統一,各類Chiplet產品接口有所不同,無法“拼接”在一起,因此行業發展受到制約。2022年3月,AMD、英特爾、臺積電、三星、美光、微軟、Meta、Google等十余家半導體、互聯網行業巨頭聯合成立了Chiplet標準聯盟,正式推出了通用Chiplet高速互聯標準“Universal Chiplet Interconnect Express”(通用芯粒互連,簡稱“UCIe”),旨在定義一個開放、可互操作的Chiplet生態系統標準。業內巨頭聯手推動Chiplet接口規范的標準化,以實現Chiplet在封裝級別的普遍互聯,構建開放的Chiplet生態系統,有助于Chiplet行業快速發展。 UCle是唯一具有裸片間接口堆棧的標準,成為Chiplet設計的首選標準。此前為應對Chiplet設計中所面臨的挑戰,行業出現了集中不同的標準,但UCle是唯一具有完整裸片間接口堆棧的標準,其他標準都沒有為協議棧提供完整裸片間接口的全面規范,大多僅關注在特定層。而且UCIe支持2D、2.5D和橋接封裝,預計未來還會支持3D封裝。 新思科技(Synosys)指出,Ucle的堆棧本身擁有三層: 協議層:最上層為協議層,通過基于流量控制單元(FLIT)的協議實現,確保最大效率和降低延遲,支持最流行的協議,包括PCI Express?(PCIe?)、Compute Express Link(CXL)和/或用戶定義的流協議; 中間層:用于對協議進行仲裁與協商,以及通過裸片間適配器進行連接管理。基于循環冗余檢查(CRC)和重試機制,該層還包括可選的錯誤糾正功能; 物理層:定義了與封裝介質的電氣接口,是電氣模擬前端(AFE)、發射器和接收器以及邊帶通道允許兩個裸片之間進行參數交換與協商的層級。邏輯PHY實現了連接初始化、訓練和校準算法,以及測試和修復功能。 圖9:Ucle產業聯盟董事會成員(資料來源:Ucle官網,東莞證券研究所) 圖10:UCIE的堆棧可分為三層(資料來源:Ucle,Synosys,東莞證券研究所) 國內廠商紛紛加入,直接受益于Chiplet發展趨勢。Ucle的提出,為集成不同制程工藝、不同廠商、不同技術的芯片提供了標準與技術支持,讓晶圓代工廠可以對不同類型的芯片進行集成,有助于Chiplet行業快速走向成熟。經過數年發展,Chiplet技術已逐漸走向商用,成為芯片廠商較為依賴的技術手段,也被認為是未來芯片行業發展的重要方向。截至目前,芯原股份、長電科技、OPPO、阿里巴巴等眾多國內知名企業已加入UCle聯盟中,直接受益于相關技術標準,共同構建Chiplet生態體系,助力行業快速發展。 Chiplet市場規模不斷擴張,預計2034年有望達到570億美元。Chiplet可在一定程度上避免摩爾定律放緩的窘境,全球半導體龍頭企業積極推進,市場規模有望實現高速增長。Omdia指出,2018年全球Chiplet市場規模約為6.45億美元,至2024年將達到58億美元,預計到2035年有望突破570億美元,2018-2035年復合增長率超過30%。 圖11:全球Chiplet芯片市場規模預測(億美元)(資料來源:Omdia,東莞證券研究所)

原文始發于微信公眾號(艾邦半導體網):Chiplet是國內半導體彎道超車的重要途徑,市場規模有望快速增長